Mạnh Quân

Writer

Ngành bán dẫn đang bước vào giai đoạn mà mỗi bước tiến đòi hỏi vượt qua những giới hạn gần như chạm đến ranh giới của vật lý nguyên tử. TSMC, Samsung và Rapidus đang chạy đua về cùng một đích, nhưng mỗi bên chọn một con đường khác nhau.

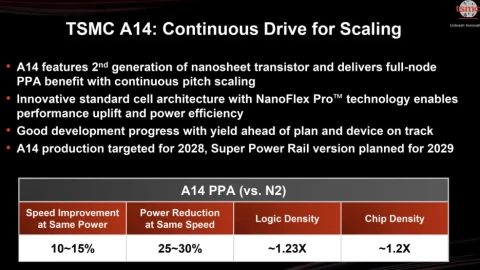

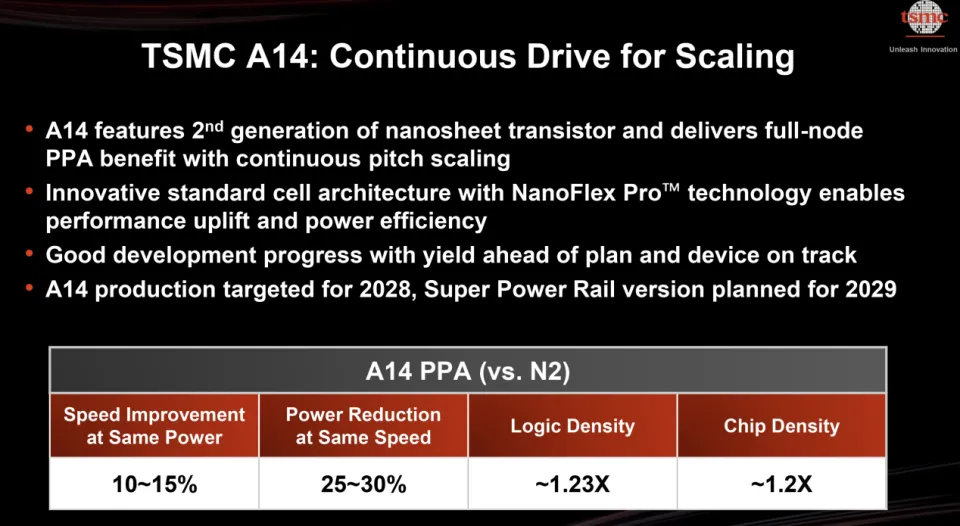

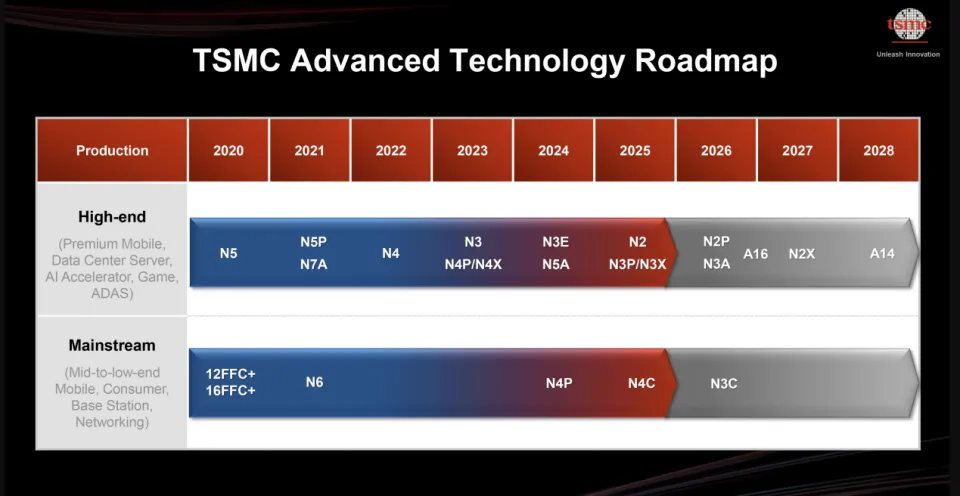

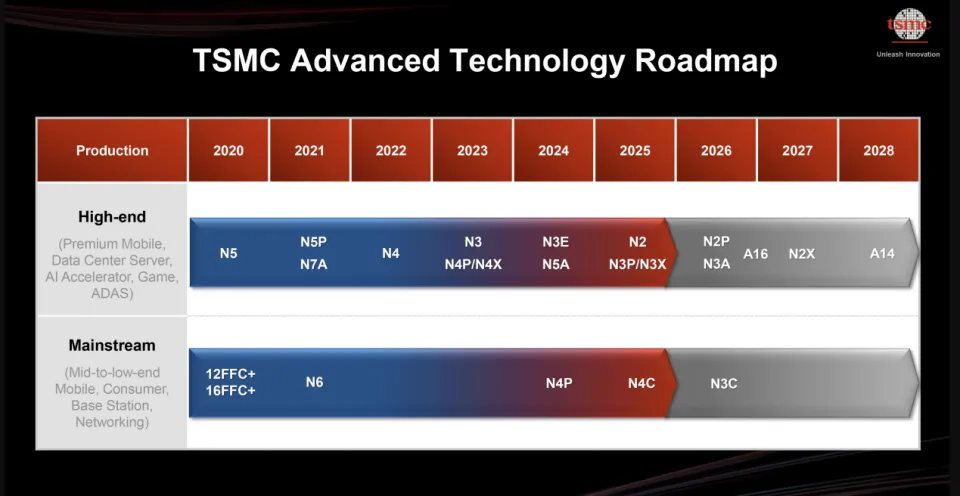

TSMC vừa xác nhận thế hệ quy trình sau 2nm sẽ mang tên "A14", với mục tiêu sản xuất thử nghiệm vào cuối năm 2027 và sản xuất hàng loạt năm 2028. Nhà máy wafer mới Fab 25 đang được xây dựng tại Khu Công nghệ Trung Đài Loan với tổng vốn đầu tư khoảng 49 tỷ USD.

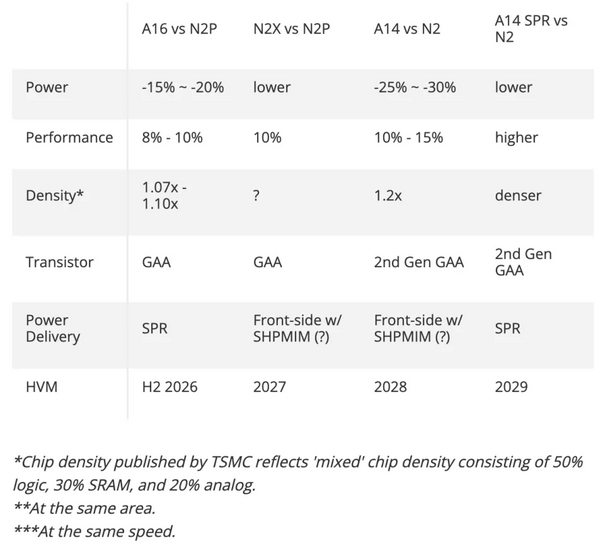

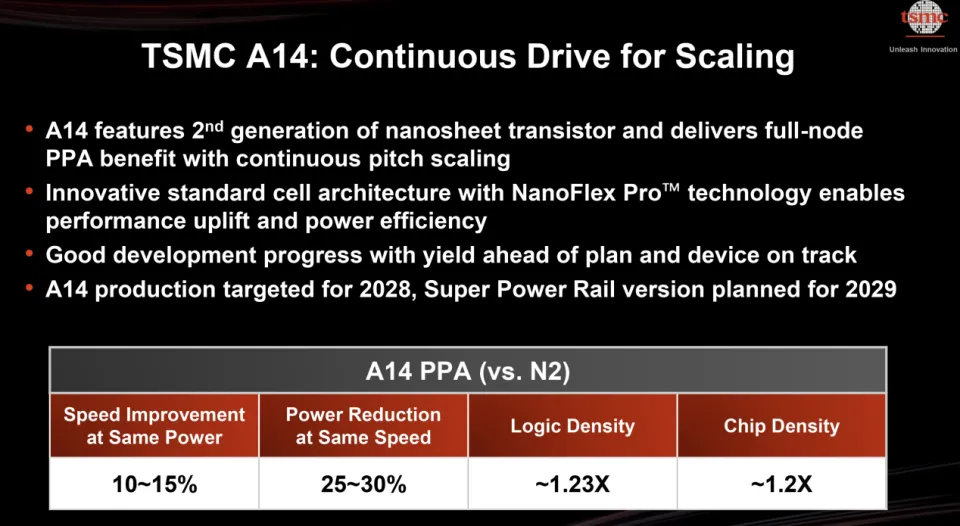

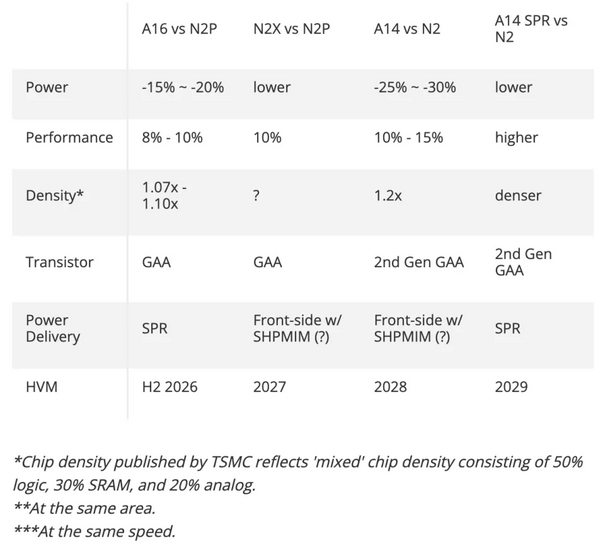

Về thông số kỹ thuật, A14 dựa trên bóng bán dẫn nanosheet GAAFET thế hệ thứ hai, mang lại hiệu năng tăng 10 đến 15% so với quy trình 2nm ở cùng mức tiêu thụ điện năng, giảm tiêu thụ điện năng 25 đến 30% ở cùng tần số, và tăng mật độ bóng bán dẫn thêm 20 đến 23%. Các chuyên gia dự báo A14 sẽ là nền tảng sản xuất cho iPhone thế hệ 2028 và chip AI máy chủ thế hệ tiếp theo.

Đáng chú ý là TSMC chọn chiến lược thận trọng: giai đoạn đầu dùng thiết bị EUV hiện có với công nghệ phơi sáng đa lớp, sau đó mới chuyển dần sang máy EUV khẩu độ số cao của ASML từ quý 3/2027. Chiến lược này trái ngược với Intel, vốn chủ trương áp dụng thiết bị thế hệ mới ngay từ đầu.

Trong khi đó, Rapidus của Nhật Bản đặt mục tiêu bắt đầu sản xuất chip thử nghiệm 2nm do khách hàng thiết kế vào cuối năm 2026, hướng tới sản xuất hàng loạt năm 2027. Giám đốc công nghệ Rapidus tuyên bố muốn thu hẹp khoảng cách với TSMC xuống còn sáu tháng ở tiến trình 1nm.

Mỗi bước thu nhỏ cũng làm tăng chi phí thiết kế chip lên hàng trăm triệu USD. Tuy nhiên, với các trung tâm dữ liệu AI tiêu thụ điện khổng lồ, lợi ích tiết kiệm điện năng dài hạn có thể bù đắp chi phí ban đầu này.

Một xu hướng quan trọng khác là các chip ngày càng mang kiến trúc đa chipset thay vì một chip đơn, cho phép kết hợp các bộ xử lý chuyên dụng khác nhau để tối ưu hóa hiệu năng. Nhưng khi số lượng chipset tăng, thách thức về kết nối, tản nhiệt và độ tin cậy hệ thống cũng tăng theo.

Như David Fried từ Lam Research nhận xét, vẫn còn nhiều dư địa để tiến lên phía trước. Câu hỏi không còn là liệu công nghệ có thể tiếp tục thu nhỏ hay không, mà là ai có đủ nguồn lực, sự kiên nhẫn và khả năng kiểm soát những biến số cực kỳ nhỏ để đi đến đích trước.

TSMC vừa xác nhận thế hệ quy trình sau 2nm sẽ mang tên "A14", với mục tiêu sản xuất thử nghiệm vào cuối năm 2027 và sản xuất hàng loạt năm 2028. Nhà máy wafer mới Fab 25 đang được xây dựng tại Khu Công nghệ Trung Đài Loan với tổng vốn đầu tư khoảng 49 tỷ USD.

Về thông số kỹ thuật, A14 dựa trên bóng bán dẫn nanosheet GAAFET thế hệ thứ hai, mang lại hiệu năng tăng 10 đến 15% so với quy trình 2nm ở cùng mức tiêu thụ điện năng, giảm tiêu thụ điện năng 25 đến 30% ở cùng tần số, và tăng mật độ bóng bán dẫn thêm 20 đến 23%. Các chuyên gia dự báo A14 sẽ là nền tảng sản xuất cho iPhone thế hệ 2028 và chip AI máy chủ thế hệ tiếp theo.

Đáng chú ý là TSMC chọn chiến lược thận trọng: giai đoạn đầu dùng thiết bị EUV hiện có với công nghệ phơi sáng đa lớp, sau đó mới chuyển dần sang máy EUV khẩu độ số cao của ASML từ quý 3/2027. Chiến lược này trái ngược với Intel, vốn chủ trương áp dụng thiết bị thế hệ mới ngay từ đầu.

Samsung nhắm mốc 1nm năm 2030, Rapidus theo sau

Samsung đang phát triển công nghệ 1nm với mục tiêu sản xuất hàng loạt vào năm 2030, sử dụng kiến trúc "Fork Sheet" mới cho phép thu nhỏ khoảng cách giữa các bóng bán dẫn GAA. Trước mắt, Samsung đang cải tiến quy trình 2nm, trong đó có biến thể SF2T để sản xuất chip AI "AI6" cho Tesla từ năm 2027 tại nhà máy Taylor, Mỹ. Hợp đồng Tesla trị giá 16,5 tỷ USD được xem là tín hiệu tích cực cho khả năng cạnh tranh công nghệ của Samsung, dù khoảng cách về thị phần với TSMC vẫn còn rất lớn.Trong khi đó, Rapidus của Nhật Bản đặt mục tiêu bắt đầu sản xuất chip thử nghiệm 2nm do khách hàng thiết kế vào cuối năm 2026, hướng tới sản xuất hàng loạt năm 2027. Giám đốc công nghệ Rapidus tuyên bố muốn thu hẹp khoảng cách với TSMC xuống còn sáu tháng ở tiến trình 1nm.

Khi vật lý trở thành rào cản

Thách thức lớn hơn không nằm ở cạnh tranh thương mại, mà ở chính giới hạn của vật lý. Ở kích thước dưới 2nm, sai lệch chỉ vài nguyên tử trong đường dẫn tín hiệu cũng có thể ảnh hưởng đến hiệu năng. Dây dẫn mỏng đến mức bất kỳ bất thường nào cũng gây chênh lệch nhiệt và dịch chuyển nhiệt, làm giảm độ tin cậy. Vật liệu như chất cản quang đòi hỏi độ tinh khiết đo bằng phần nghìn tỷ.Mỗi bước thu nhỏ cũng làm tăng chi phí thiết kế chip lên hàng trăm triệu USD. Tuy nhiên, với các trung tâm dữ liệu AI tiêu thụ điện khổng lồ, lợi ích tiết kiệm điện năng dài hạn có thể bù đắp chi phí ban đầu này.

Một xu hướng quan trọng khác là các chip ngày càng mang kiến trúc đa chipset thay vì một chip đơn, cho phép kết hợp các bộ xử lý chuyên dụng khác nhau để tối ưu hóa hiệu năng. Nhưng khi số lượng chipset tăng, thách thức về kết nối, tản nhiệt và độ tin cậy hệ thống cũng tăng theo.

Như David Fried từ Lam Research nhận xét, vẫn còn nhiều dư địa để tiến lên phía trước. Câu hỏi không còn là liệu công nghệ có thể tiếp tục thu nhỏ hay không, mà là ai có đủ nguồn lực, sự kiên nhẫn và khả năng kiểm soát những biến số cực kỳ nhỏ để đi đến đích trước.