myle.vnreview

Writer

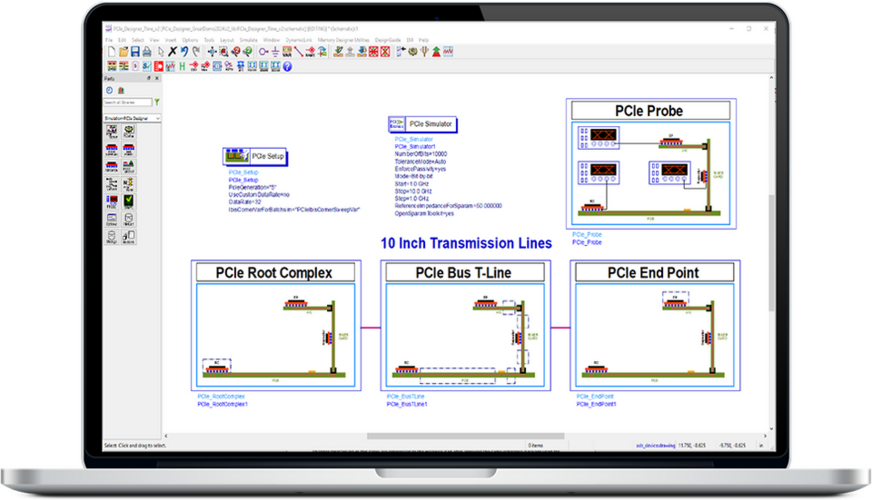

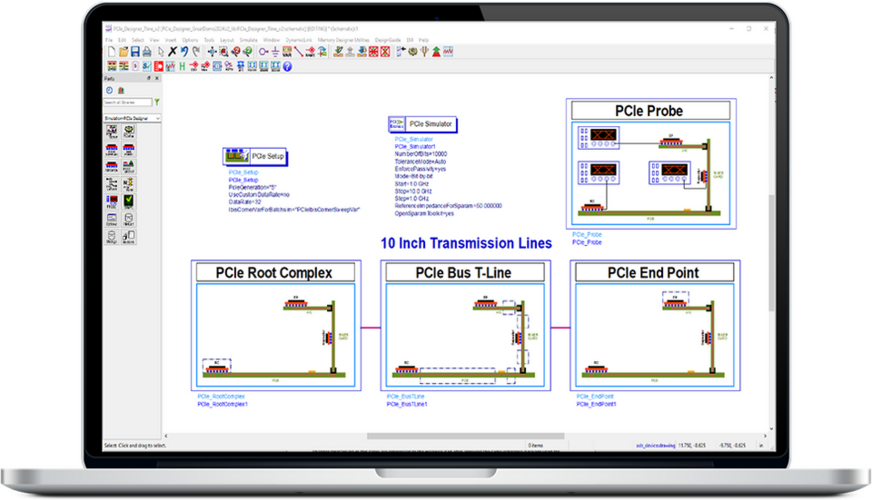

Keysight Technologies vừa giới thiệu System Designer for PCIe, sản phẩm mới thuộc dòng sản phẩm Advanced Design System (ADS), có chức năng hỗ trợ quy trình làm việc mô phỏng dựa trên tiêu chuẩn công nghiệp dành cho thiết kế kỹ thuật số tốc độ cao, tần số cao.

System Designer for PCIe cung cấp môi trường thiết kế thông minh dùng để mô hình hóa và mô phỏng các hệ thống theo chuẩn Peripheral Component Interconnect Express (PCIe) Gen5 và Gen6 mới nhất. Keysight cũng đang cải thiện nền tảng tự động hóa thiết kế điện tử (EDA) của mình bằng cách bổ sung các tính năng mới vào công cụ Chiplet PHY Designer hiện có, giúp ước tính hiệu suất biên độ liên kết chiplet die-to-die và phép đo tuân thủ chức năng truyền điện áp Voltage Transfer Function (VTF) chính xác hơn.

PCIe là một tiêu chuẩn giao diện đa năng và thiết yếu trong nhiều phân khúc của ngành công nghiệp điện tử nhờ khả năng truyền dữ liệu tốc độ cao, khả năng mở rộng và khả năng thích ứng. Tiêu chuẩn này được áp dụng rộng rãi, từ các thiết bị điện tử tiêu dùng hàng ngày đến các ứng dụng chuyên biệt trong máy tính hiệu suất cao và hệ thống cơ sở hạ tầng trọng yếu.

Các thiết kế PCIe phức tạp hỗ trợ nhiều hệ thống đa liên kết và đa làn, đòi hỏi thực hiện bài toán phân tích phức tạp giữa RootComplex và End-Point, đôi khi kết hợp bộ lặp giữa kênh. Mặc dù các nhà thiết kế tốn rất nhiều thời gian để chuẩn bị, các phép mô phỏng vẫn thường xuyên mắc lỗi. Các mô phỏng thường thiếu các mô hình mô phỏng giao diện thuật toán (AMI) đặc thù của nhà cung cấp, là yêu cầu bắt buộc trong giai đoạn đầu của chu kỳ thiết kế để khám phá không gian thiết kế. Các nhà thiết kế cũng cần đảm bảo rằng thiết kế nguyên mẫu của họ có thể vượt qua kiểm thử tuân thủ trước khi chuyển sang chế tạo phần cứng.

Các tính năng cải thiện năng suất, quy trình làm việc và tuân thủ

● System Designer for PCIe sử dụng môi trường thiết kế thông minh để tự động thiết lập các hệ thống PCIe đa liên kết, đa làn và đa cấp (PAM4). Giải pháp này đơn giản hóa việc thiết lập mô phỏng và rút ngắn thời gian đưa ra nhận định đầu tiên.

● Bộ tạo mô hình AMI PCIe, hỗ trợ điều chế NRZ và PAM4, giúp nhanh chóng tạo mô hình AMI cần thiết cho việc phân tích hệ thống PCIe. Bộ xây dựng mô hình AMI Model Builder có tính năng hướng dẫn, giúp các nhà thiết kế quy trình tạo mô hình AMI cho cả máy phát (Tx) và máy thu (Rx) một cách nhanh chóng và hiệu quả.

● Đo kiểm tuân thủ ảo đơn giản, trên cơ sở mô phỏng giúp cho đội ngũ thiết kế đảm bảo chất lượng thiết kế. Quy trình kiểm tra tuân thủ PCIe tích hợp dựa trên mô phỏng giúp giảm chi phí thiết kế bằng cách giảm thiểu các lần thiết kế lại và rút ngắn thời gian đưa sản phẩm ra thị trường.

Các tính năng cải tiến của Chiplet PHY Designer

● Chiplet PHY Designer là giải pháp mô phỏng đầu tiên của ngành EDA dành cho các tiêu chuẩn Universal Chiplet Interconnect Express (UCIe), cho phép dự đoán quỹ công suất liên kết giữa các chip, VTF để phân tích sự tuân thủ của kênh và khả năng chuyển tiếp xung nhịp. Chiplet PHY Designer bao gồm các tính năng khám phá thiết kế và tạo báo cáo mới, giúp đẩy nhanh quá trình phân tích tính toàn vẹn của tín hiệu và xác minh tuân thủ để cải thiện năng suất thiết kế và thời gian đưa sản phẩm ra thị trường.

System Designer for PCIe cung cấp môi trường thiết kế thông minh dùng để mô hình hóa và mô phỏng các hệ thống theo chuẩn Peripheral Component Interconnect Express (PCIe) Gen5 và Gen6 mới nhất. Keysight cũng đang cải thiện nền tảng tự động hóa thiết kế điện tử (EDA) của mình bằng cách bổ sung các tính năng mới vào công cụ Chiplet PHY Designer hiện có, giúp ước tính hiệu suất biên độ liên kết chiplet die-to-die và phép đo tuân thủ chức năng truyền điện áp Voltage Transfer Function (VTF) chính xác hơn.

PCIe là một tiêu chuẩn giao diện đa năng và thiết yếu trong nhiều phân khúc của ngành công nghiệp điện tử nhờ khả năng truyền dữ liệu tốc độ cao, khả năng mở rộng và khả năng thích ứng. Tiêu chuẩn này được áp dụng rộng rãi, từ các thiết bị điện tử tiêu dùng hàng ngày đến các ứng dụng chuyên biệt trong máy tính hiệu suất cao và hệ thống cơ sở hạ tầng trọng yếu.

Các thiết kế PCIe phức tạp hỗ trợ nhiều hệ thống đa liên kết và đa làn, đòi hỏi thực hiện bài toán phân tích phức tạp giữa RootComplex và End-Point, đôi khi kết hợp bộ lặp giữa kênh. Mặc dù các nhà thiết kế tốn rất nhiều thời gian để chuẩn bị, các phép mô phỏng vẫn thường xuyên mắc lỗi. Các mô phỏng thường thiếu các mô hình mô phỏng giao diện thuật toán (AMI) đặc thù của nhà cung cấp, là yêu cầu bắt buộc trong giai đoạn đầu của chu kỳ thiết kế để khám phá không gian thiết kế. Các nhà thiết kế cũng cần đảm bảo rằng thiết kế nguyên mẫu của họ có thể vượt qua kiểm thử tuân thủ trước khi chuyển sang chế tạo phần cứng.

Các tính năng cải thiện năng suất, quy trình làm việc và tuân thủ

● System Designer for PCIe sử dụng môi trường thiết kế thông minh để tự động thiết lập các hệ thống PCIe đa liên kết, đa làn và đa cấp (PAM4). Giải pháp này đơn giản hóa việc thiết lập mô phỏng và rút ngắn thời gian đưa ra nhận định đầu tiên.

● Bộ tạo mô hình AMI PCIe, hỗ trợ điều chế NRZ và PAM4, giúp nhanh chóng tạo mô hình AMI cần thiết cho việc phân tích hệ thống PCIe. Bộ xây dựng mô hình AMI Model Builder có tính năng hướng dẫn, giúp các nhà thiết kế quy trình tạo mô hình AMI cho cả máy phát (Tx) và máy thu (Rx) một cách nhanh chóng và hiệu quả.

● Đo kiểm tuân thủ ảo đơn giản, trên cơ sở mô phỏng giúp cho đội ngũ thiết kế đảm bảo chất lượng thiết kế. Quy trình kiểm tra tuân thủ PCIe tích hợp dựa trên mô phỏng giúp giảm chi phí thiết kế bằng cách giảm thiểu các lần thiết kế lại và rút ngắn thời gian đưa sản phẩm ra thị trường.

Các tính năng cải tiến của Chiplet PHY Designer

● Chiplet PHY Designer là giải pháp mô phỏng đầu tiên của ngành EDA dành cho các tiêu chuẩn Universal Chiplet Interconnect Express (UCIe), cho phép dự đoán quỹ công suất liên kết giữa các chip, VTF để phân tích sự tuân thủ của kênh và khả năng chuyển tiếp xung nhịp. Chiplet PHY Designer bao gồm các tính năng khám phá thiết kế và tạo báo cáo mới, giúp đẩy nhanh quá trình phân tích tính toàn vẹn của tín hiệu và xác minh tuân thủ để cải thiện năng suất thiết kế và thời gian đưa sản phẩm ra thị trường.