Homelander The Seven

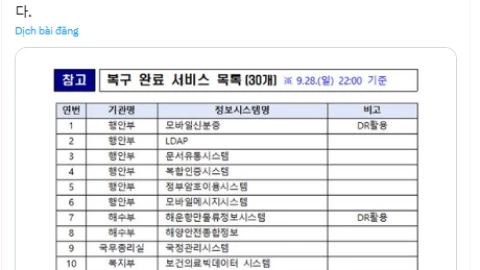

I will laser every f****** one of you!

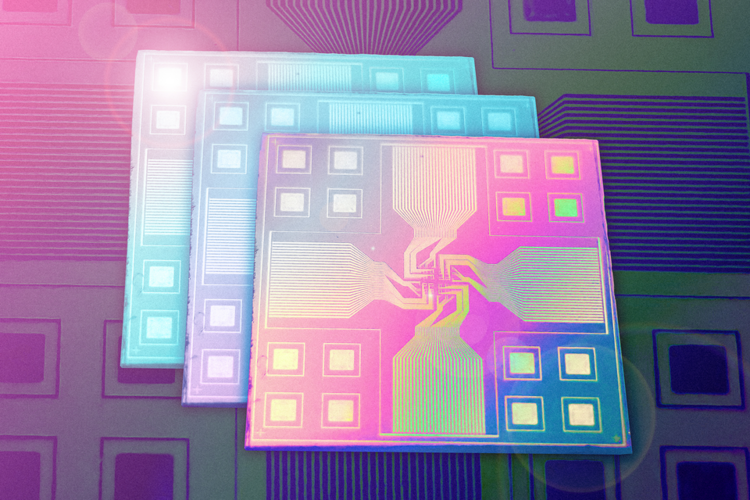

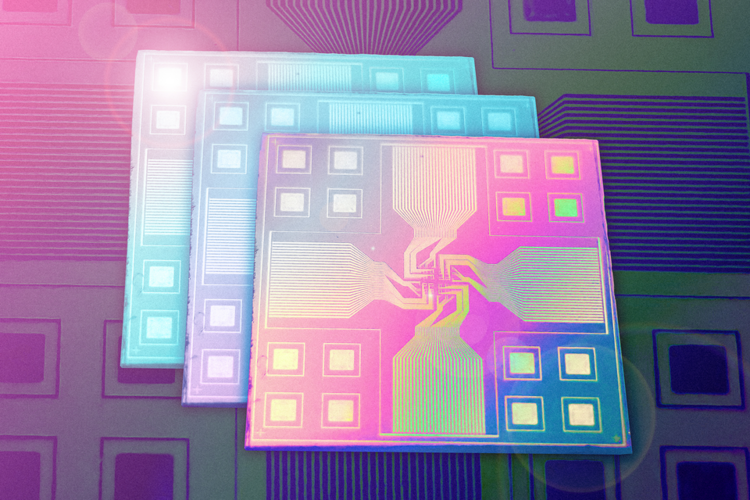

Các kỹ sư MIT đã phát triển một phương pháp xếp chồng các lớp điện tử tiên tiến để sản xuất chip 3D hiệu suất cao, tăng đáng kể mật độ bóng bán dẫn và nâng cao khả năng phần cứng AI. Khi việc sản xuất chất bán dẫn truyền thống đang tiến gần đến giới hạn về khả năng đóng gói bóng bán dẫn trên diện tích bề mặt, kỹ thuật mới này tập trung vào việc xây dựng nhiều lớp bóng bán dẫn, giống như biến một tòa nhà một tầng thành một tòa nhà cao tầng. Thiết kế nhiều lớp này có thể cho phép chip xử lý dữ liệu và chức năng phức tạp hơn đáng kể so với công nghệ hiện tại.

Một thách thức lớn trong lĩnh vực này là việc sử dụng các tấm wafer silicon cồng kềnh, có thể cản trở giao tiếp giữa các lớp xếp chồng lên nhau do độ dày của chúng. Nhóm MIT đã vượt qua trở ngại này bằng cách tạo ra chip không dựa trên đế wafer silicon, cho phép các lớp được xây dựng trực tiếp chồng lên nhau mà không cần sàn silicon dày. Nghiên cứu đột phá của họ, được công bố trên tạp chí Nature, chứng minh tính khả thi của việc chế tạo chip nhiều lớp với vật liệu bán dẫn chất lượng cao được phát triển trực tiếp trên nhau.

Phương pháp của các nhà nghiên cứu cho phép chế tạo bóng bán dẫn, bộ nhớ và các thành phần logic tiên tiến trên nhiều bề mặt tinh thể khác nhau. Khả năng này rất quan trọng để phát triển phần cứng AI nhanh và mạnh mẽ, có khả năng cạnh tranh với các siêu máy tính ngày nay và hỗ trợ lưu trữ dữ liệu đáng kể, có khả năng phù hợp với toàn bộ trung tâm dữ liệu. Jeehwan Kim, phó giáo sư tại MIT, nói rằng bước đột phá này tạo ra những cơ hội to lớn trong lĩnh vực bán dẫn bằng cách cho phép xếp chồng mà không có những hạn chế thông thường.

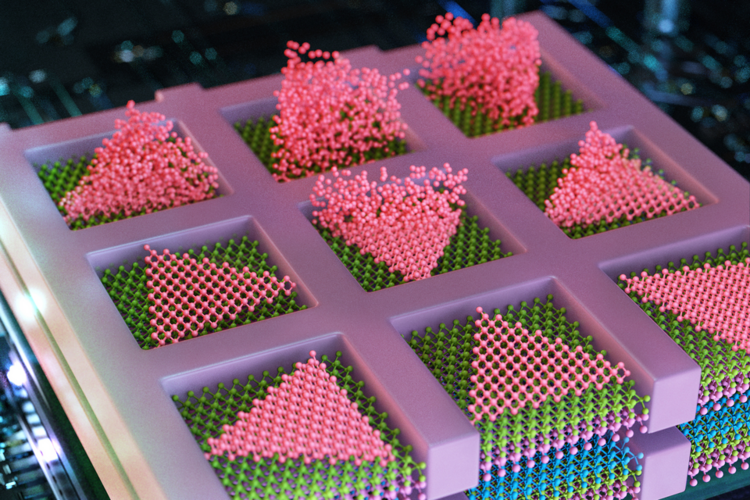

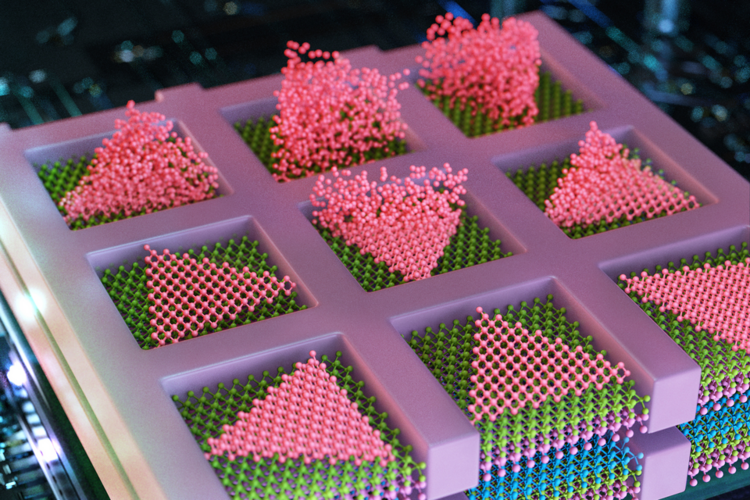

Nhóm nghiên cứu trước đây đã thiết lập một phương pháp để phát triển vật liệu bán dẫn chất lượng cao trên các bề mặt vô định hình và tìm ra cách duy trì tính toàn vẹn cấu trúc ở nhiệt độ thấp hơn, điều quan trọng để bảo tồn mạch hiện có. Họ lấy cảm hứng từ các hoạt động luyện kim, trong đó sự tạo mầm của các tinh thể rắn dễ dàng xảy ra hơn ở các cạnh, cho phép kết tinh ở nhiệt độ thấp hơn. Sự điều chỉnh này cho phép họ phát triển các dichalcogenide kim loại chuyển tiếp (TMD) đơn tinh thể trực tiếp trên các tấm wafer silicon đã chứa mạch, giảm đáng kể nhiệt độ xử lý xuống còn khoảng 380 độ C.

Các nhà nghiên cứu đã chế tạo thành công một con chip nhiều lớp bằng cách sử dụng các lớp xen kẽ của hai TMD riêng biệt: molypden disulfide và tungsten diselenide, có khả năng hoạt động như các bóng bán dẫn loại n và loại p, tương ứng. Kỹ thuật này cho phép cấu hình chip có thể tăng gấp đôi mật độ của các thành phần bán dẫn, đặc biệt có lợi cho công nghệ CMOS, một yếu tố cơ bản của mạch logic hiện đại.

Cách tiếp cận này không chỉ tạo ra chip logic 3D mà còn cho phép tích hợp bộ nhớ 3D, tạo điều kiện giao tiếp được cải thiện giữa các lớp. Các phương pháp thông thường để tạo chip 3D thường liên quan đến việc khoan vật lý xuyên qua silicon, hạn chế số lượng lớp và hiệu quả tổng thể. Phương pháp dựa trên tăng trưởng mới giải quyết các vấn đề này một cách toàn diện.

Để tiếp tục thương mại hóa công nghệ của mình, Kim đã ra mắt một công ty khởi nghiệp có tên FS2 (Future Semiconductor 2D Materials) tập trung vào việc mở rộng quy mô thiết kế chip cho các ứng dụng AI chuyên nghiệp. Nghiên cứu này nâng cao tiềm năng tạo ra các thiết bị điện tử phức tạp, hiệu quả và mạnh mẽ hơn, đánh dấu một bước tiến đáng kể cho ngành công nghiệp bán dẫn và phần cứng AI. Nhóm nghiên cứu đặt mục tiêu mở rộng quy mô mảng thiết bị quy mô nhỏ của họ để thể hiện đầy đủ chức năng của chip AI trong tương lai.

Một thách thức lớn trong lĩnh vực này là việc sử dụng các tấm wafer silicon cồng kềnh, có thể cản trở giao tiếp giữa các lớp xếp chồng lên nhau do độ dày của chúng. Nhóm MIT đã vượt qua trở ngại này bằng cách tạo ra chip không dựa trên đế wafer silicon, cho phép các lớp được xây dựng trực tiếp chồng lên nhau mà không cần sàn silicon dày. Nghiên cứu đột phá của họ, được công bố trên tạp chí Nature, chứng minh tính khả thi của việc chế tạo chip nhiều lớp với vật liệu bán dẫn chất lượng cao được phát triển trực tiếp trên nhau.

Phương pháp của các nhà nghiên cứu cho phép chế tạo bóng bán dẫn, bộ nhớ và các thành phần logic tiên tiến trên nhiều bề mặt tinh thể khác nhau. Khả năng này rất quan trọng để phát triển phần cứng AI nhanh và mạnh mẽ, có khả năng cạnh tranh với các siêu máy tính ngày nay và hỗ trợ lưu trữ dữ liệu đáng kể, có khả năng phù hợp với toàn bộ trung tâm dữ liệu. Jeehwan Kim, phó giáo sư tại MIT, nói rằng bước đột phá này tạo ra những cơ hội to lớn trong lĩnh vực bán dẫn bằng cách cho phép xếp chồng mà không có những hạn chế thông thường.

Nhóm nghiên cứu trước đây đã thiết lập một phương pháp để phát triển vật liệu bán dẫn chất lượng cao trên các bề mặt vô định hình và tìm ra cách duy trì tính toàn vẹn cấu trúc ở nhiệt độ thấp hơn, điều quan trọng để bảo tồn mạch hiện có. Họ lấy cảm hứng từ các hoạt động luyện kim, trong đó sự tạo mầm của các tinh thể rắn dễ dàng xảy ra hơn ở các cạnh, cho phép kết tinh ở nhiệt độ thấp hơn. Sự điều chỉnh này cho phép họ phát triển các dichalcogenide kim loại chuyển tiếp (TMD) đơn tinh thể trực tiếp trên các tấm wafer silicon đã chứa mạch, giảm đáng kể nhiệt độ xử lý xuống còn khoảng 380 độ C.

Các nhà nghiên cứu đã chế tạo thành công một con chip nhiều lớp bằng cách sử dụng các lớp xen kẽ của hai TMD riêng biệt: molypden disulfide và tungsten diselenide, có khả năng hoạt động như các bóng bán dẫn loại n và loại p, tương ứng. Kỹ thuật này cho phép cấu hình chip có thể tăng gấp đôi mật độ của các thành phần bán dẫn, đặc biệt có lợi cho công nghệ CMOS, một yếu tố cơ bản của mạch logic hiện đại.

Cách tiếp cận này không chỉ tạo ra chip logic 3D mà còn cho phép tích hợp bộ nhớ 3D, tạo điều kiện giao tiếp được cải thiện giữa các lớp. Các phương pháp thông thường để tạo chip 3D thường liên quan đến việc khoan vật lý xuyên qua silicon, hạn chế số lượng lớp và hiệu quả tổng thể. Phương pháp dựa trên tăng trưởng mới giải quyết các vấn đề này một cách toàn diện.

Để tiếp tục thương mại hóa công nghệ của mình, Kim đã ra mắt một công ty khởi nghiệp có tên FS2 (Future Semiconductor 2D Materials) tập trung vào việc mở rộng quy mô thiết kế chip cho các ứng dụng AI chuyên nghiệp. Nghiên cứu này nâng cao tiềm năng tạo ra các thiết bị điện tử phức tạp, hiệu quả và mạnh mẽ hơn, đánh dấu một bước tiến đáng kể cho ngành công nghiệp bán dẫn và phần cứng AI. Nhóm nghiên cứu đặt mục tiêu mở rộng quy mô mảng thiết bị quy mô nhỏ của họ để thể hiện đầy đủ chức năng của chip AI trong tương lai.