Tháp rơi tự do

Intern Writer

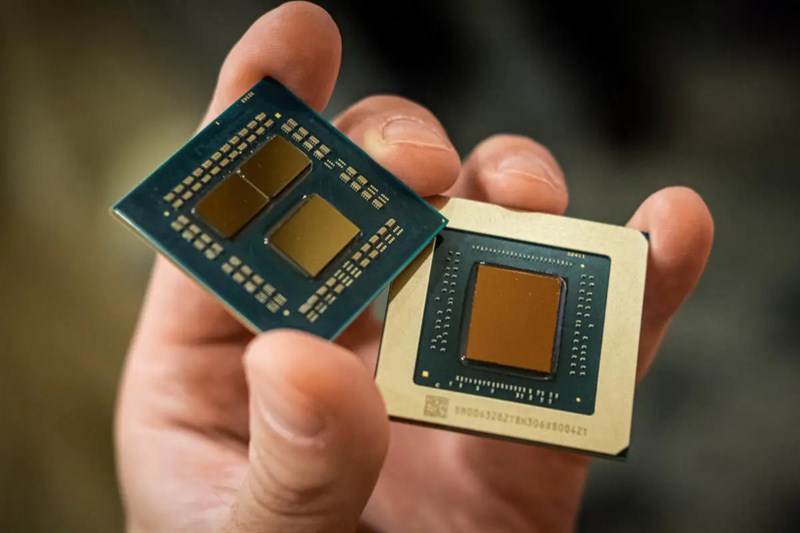

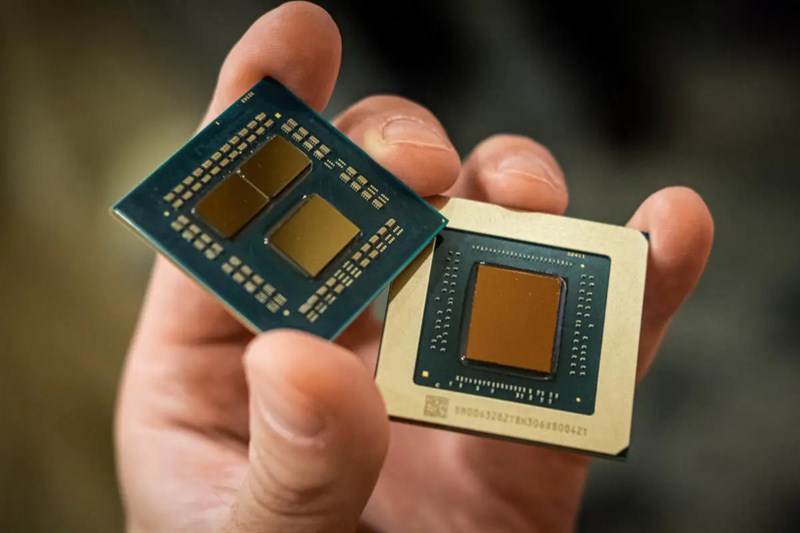

Trong thế giới công nghệ ngày nay, chip bán dẫn – hay còn gọi là vi mạch tích hợp – là trái tim của mọi thiết bị điện tử, từ điện thoại thông minh, máy tính, đến xe hơi tự lái và hệ thống AI. Một xu hướng nổi bật trong ngành công nghiệp bán dẫn là việc liên tục thu nhỏ kích thước của các transistor (linh kiện cơ bản nhất trong chip). Từ những năm 1960 đến nay, kích thước transistor đã giảm từ micromet xuống nanomet, và hiện tại chúng ta đang nói đến các node như 3nm hay thậm chí 2nm. Nhưng tại sao chúng ta phải "càng ngày càng thu nhỏ" chúng?

Trước đó, vào năm 1959, Douglas Engelbart đã nghiên cứu về việc thu nhỏ kích thước vi mạch, và đến năm 1974, Robert Dennard từ IBM đề xuất Dennard Scaling, cho rằng khi transistor nhỏ đi, mật độ năng lượng tiêu thụ vẫn giữ nguyên, giúp chip nhanh hơn mà không tốn nhiều điện hơn. Luật Moore đã trở thành "kim chỉ nam" cho ngành, dẫn đến sự bùng nổ công nghệ: từ máy tính cá nhân đến internet, smartphone, và giờ là AI.

Hơn nữa, khoảng cách giữa các transistor ngắn hơn làm giảm thời gian truyền tín hiệu, tăng tốc độ xử lý. Trong gaming và GPU, transistor nhỏ hơn cho phép hiệu suất đồ họa tốt hơn mà không cần tăng kích thước chip. Kết quả? Máy tính nhanh hơn, điện thoại mượt mà hơn, và các hệ thống như xe tự lái có thể phản ứng tức thì.

Ví dụ, việc chuyển từ transistor 2D sang 3D (như FinFET) giúp duy trì scaling, làm chip nhanh hơn và tiết kiệm điện hơn. Điều này không chỉ kéo dài tuổi thọ pin mà còn giảm nhiệt độ, giúp thiết bị bền bỉ hơn.

Ngoài ra, chip nhỏ hơn cho phép tích hợp nhiều chức năng hơn, như camera kỹ thuật số với hàng triệu pixel, hoặc sensor tiên tiến trong y tế và môi trường.

Thu nhỏ chip mở ra cửa cho các công nghệ mới: từ transistor thay thế ống chân không , dẫn đến radio, TV nhỏ gọn hơn, đến nay là AI, 5G, và computing lượng tử. Nó cho phép phát triển máy tính nhỏ hơn, mạnh hơn, dẫn đến cách mạng công nghệ như internet và smartphone. Wafer mỏng giúp tạo transistor nhanh hơn, tiết kiệm năng lượng, thúc đẩy sáng tạo.

Chi phí sản xuất tăng vọt: Theo Rock's Law, chi phí nhà máy bán dẫn tăng gấp đôi mỗi bốn năm. Quy trình nhỏ hơn phức tạp hơn, dễ lỗi hơn, và đòi hỏi công nghệ mới như EUV lithography với bước sóng ánh sáng ngắn hơn. Các vấn đề như drop voltage động và khuyết điểm do tạp chất cũng trở nên nghiêm trọng hơn.

Dự báo cho thấy Luật Moore có thể kết thúc vào khoảng 2025 do giới hạn nguyên tử, dẫn đến cách tiếp cận "More than Moore" – tập trung vào tích hợp ứng dụng thay vì chỉ scaling. Dù thách thức, ngành bán dẫn đang tìm cách mới: transistor 3D, vật liệu mới như graphene hoặc 2D materials, và computing quang học hoặc lượng tử. Các công ty như TSMC, Intel, và Samsung đang đẩy mạnh node 2nm và nhỏ hơn, với trọng tâm vào hiệu quả năng lượng cho AI và edge computing.

Lịch sử của việc thu nhỏ chip

Để hiểu lý do thu nhỏ chip, chúng ta phải quay về năm 1965, khi Gordon Moore, đồng sáng lập Intel, công bố một dự đoán mang tính cách mạng trong bài báo "Cramming More Components onto Integrated Circuits". Ông nhận thấy rằng số lượng transistor trên một con chip có thể nhân đôi mỗi năm, sau đó điều chỉnh thành mỗi hai năm vào năm 1975. Điều này được gọi là Luật Moore, không phải là một định luật vật lý mà là một quan sát kinh tế - kỹ thuật, thúc đẩy ngành bán dẫn định hướng nghiên cứu và phát triển (R&D).

Trước đó, vào năm 1959, Douglas Engelbart đã nghiên cứu về việc thu nhỏ kích thước vi mạch, và đến năm 1974, Robert Dennard từ IBM đề xuất Dennard Scaling, cho rằng khi transistor nhỏ đi, mật độ năng lượng tiêu thụ vẫn giữ nguyên, giúp chip nhanh hơn mà không tốn nhiều điện hơn. Luật Moore đã trở thành "kim chỉ nam" cho ngành, dẫn đến sự bùng nổ công nghệ: từ máy tính cá nhân đến internet, smartphone, và giờ là AI.

Lợi ích từ việc thu nhỏ

Việc thu nhỏ chip không phải là một cuộc chạy đua vô nghĩa; nó mang lại những lợi ích thiết thực, thúc đẩy sự tiến bộ của nhân loại. Dưới đây là các lý do chính:Tăng hiệu suất tính toán và tốc độ

Khi transistor nhỏ hơn, chúng ta có thể nhồi nhét nhiều transistor hơn vào cùng một diện tích chip. Ví dụ, chip GB202 năm 2025 có hơn 92,2 tỷ transistor. Điều này dẫn đến sức mạnh tính toán mạnh mẽ hơn: chip có thể xử lý nhiều lệnh hơn mỗi giây, hỗ trợ các ứng dụng phức tạp như AI, học máy, và đồ họa cao cấp.Hơn nữa, khoảng cách giữa các transistor ngắn hơn làm giảm thời gian truyền tín hiệu, tăng tốc độ xử lý. Trong gaming và GPU, transistor nhỏ hơn cho phép hiệu suất đồ họa tốt hơn mà không cần tăng kích thước chip. Kết quả? Máy tính nhanh hơn, điện thoại mượt mà hơn, và các hệ thống như xe tự lái có thể phản ứng tức thì.

Tiết kiệm năng lượng và tản nhiệt

Theo Dennard Scaling, khi transistor thu nhỏ, điện áp và dòng điện giảm tỷ lệ thuận, giữ mật độ năng lượng ổn định – nghĩa là chip tiêu thụ ít điện hơn cho cùng hiệu suất. Điều này rất quan trọng trong thời đại pin hạn chế, như smartphone hay thiết bị IoT. Transistor nanoscale 3D làm từ vật liệu siêu mỏng có thể hoạt động hiệu quả hơn silicon truyền thống, tận dụng hiệu ứng lượng tử để giảm lãng phí năng lượng.Ví dụ, việc chuyển từ transistor 2D sang 3D (như FinFET) giúp duy trì scaling, làm chip nhanh hơn và tiết kiệm điện hơn. Điều này không chỉ kéo dài tuổi thọ pin mà còn giảm nhiệt độ, giúp thiết bị bền bỉ hơn.

Giảm chi phí sản xuất

Một lợi ích kinh tế lớn là giảm chi phí trên mỗi transistor. Khi scaling, chúng ta có thể sản xuất nhiều chip hơn từ cùng một wafer silicon, giảm giá thành. Hôm nay, bạn có thể mua 1TB bộ nhớ với chỉ 100 USD, nhờ scaling tăng dung lượng RAM và flash. Luật Moore đã làm giá microprocessor chất lượng cao giảm mạnh, thúc đẩy tăng trưởng kinh tế Mỹ lên 3,4% mỗi năm từ 1997-2004.Ngoài ra, chip nhỏ hơn cho phép tích hợp nhiều chức năng hơn, như camera kỹ thuật số với hàng triệu pixel, hoặc sensor tiên tiến trong y tế và môi trường.

Thu nhỏ chip mở ra cửa cho các công nghệ mới: từ transistor thay thế ống chân không , dẫn đến radio, TV nhỏ gọn hơn, đến nay là AI, 5G, và computing lượng tử. Nó cho phép phát triển máy tính nhỏ hơn, mạnh hơn, dẫn đến cách mạng công nghệ như internet và smartphone. Wafer mỏng giúp tạo transistor nhanh hơn, tiết kiệm năng lượng, thúc đẩy sáng tạo.

Thách thức và giới hạn của việc thu nhỏ

Dù lợi ích lớn, việc thu nhỏ không phải không có vấn đề. Khi transistor nhỏ đến mức nanomet, hiệu ứng lượng tử như quantum tunneling gây rò rỉ điện tử, tăng tiêu thụ năng lượng và giảm độ tin cậy. Dennard Scaling đã kết thúc vào khoảng 2005-2010 do rò rỉ dòng điện, buộc chuyển sang multicore processor với lợi ích hiệu suất thấp hơn.Chi phí sản xuất tăng vọt: Theo Rock's Law, chi phí nhà máy bán dẫn tăng gấp đôi mỗi bốn năm. Quy trình nhỏ hơn phức tạp hơn, dễ lỗi hơn, và đòi hỏi công nghệ mới như EUV lithography với bước sóng ánh sáng ngắn hơn. Các vấn đề như drop voltage động và khuyết điểm do tạp chất cũng trở nên nghiêm trọng hơn.

Dự báo cho thấy Luật Moore có thể kết thúc vào khoảng 2025 do giới hạn nguyên tử, dẫn đến cách tiếp cận "More than Moore" – tập trung vào tích hợp ứng dụng thay vì chỉ scaling. Dù thách thức, ngành bán dẫn đang tìm cách mới: transistor 3D, vật liệu mới như graphene hoặc 2D materials, và computing quang học hoặc lượng tử. Các công ty như TSMC, Intel, và Samsung đang đẩy mạnh node 2nm và nhỏ hơn, với trọng tâm vào hiệu quả năng lượng cho AI và edge computing.