Homelander The Seven

I will laser every f****** one of you!

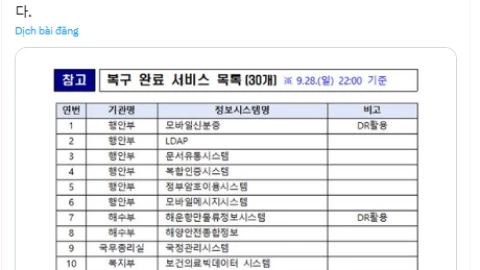

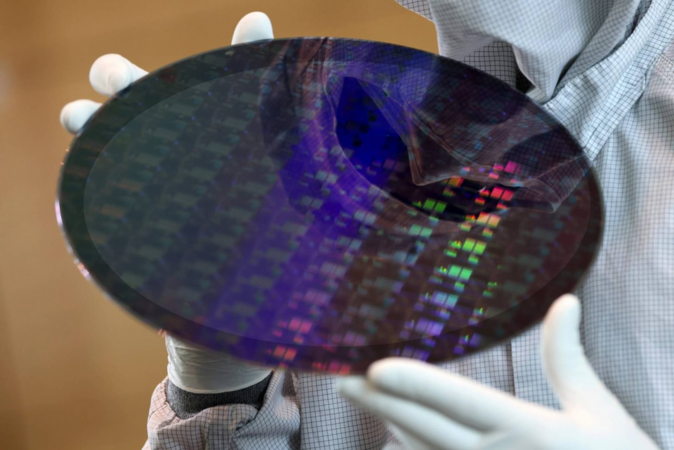

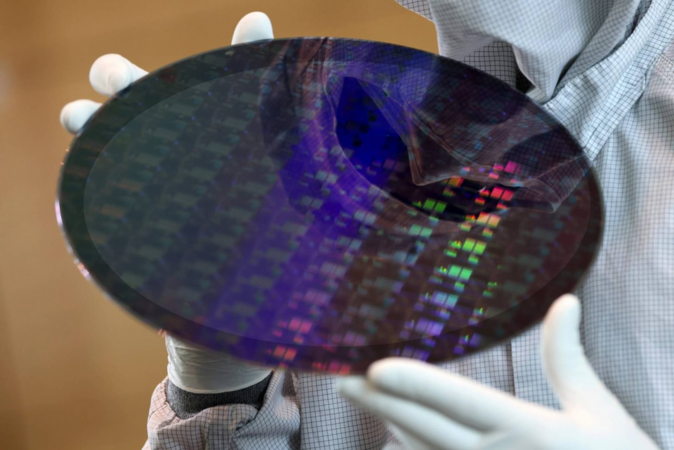

Có vẻ như gã khổng lồ Đài Loan sẽ không sớm tham gia 'cuộc đua' High-NA EUV. Thông tin mới tiết lộ cho thấy công ty này sẽ bỏ qua công nghệ quang khắc tiên tiến này cho quy trình A14 của mình.

Trong nhiều năm, TSMC luôn là nhà tiên phong và thường là người tạo ra xu hướng trong việc áp dụng các yếu tố mới trong ngành bán dẫn. Nhưng giờ đây, có vẻ như công ty sẽ bỏ qua việc sử dụng công cụ quang khắc High-NA EUV cho quy trình A14 của mình, mà sẽ dựa vào công nghệ EUV 0.33-NA thông thường hơn. Thông tin này được tiết lộ tại Hội nghị chuyên đề Công nghệ Bắc Mỹ (NA Technology Symposium), nơi Phó Chủ tịch Cấp cao (SVP) của TSMC, Kevin Zhang, đã công bố về sự phát triển này (thông qua Bits & Chips). Với điều này, có thể nói rằng Intel Foundry và một số nhà sản xuất DRAM hiện đang có lợi thế 'công nghệ' hơn so với TSMC.

Phát biểu của ông Kevin Zhang tại sự kiện:

Vâng, lý do chính khiến TSMC coi High-NA là không quá cần thiết cho quy trình A14 là vì với các công cụ quang khắc liên quan, gã khổng lồ Đài Loan có thể phải đối mặt với chi phí tăng gấp 2,5 lần so với các phương pháp EUV truyền thống, và điều này cuối cùng sẽ làm cho nút A14 trở nên đắt đỏ hơn nhiều trong sản xuất, đồng nghĩa với việc việc áp dụng nó vào các sản phẩm tiêu dùng sẽ trở nên khó khăn. Gã khổng lồ Đài Loan đang dựa vào thiết kế và khả năng của chip hiện tại, nhưng điều này chắc chắn không có nghĩa là công ty sẽ không sử dụng High-NA EUV cho các quy trình trong tương lai, vì họ có kế hoạch sử dụng nó cho nút A14P.

Một trong những lý do khác khiến High-NA đẩy chi phí lên cao là node A14 của TSMC sẽ yêu cầu nhiều mặt nạ cho một lớp thiết kế chip duy nhất hơn, việc sử dụng các công cụ quang khắc mới nhất đơn giản có nghĩa là gã khổng lồ Đài Loan đang làm tăng chi phí mà không thu được nhiều lợi ích. Thay vào đó, bằng cách tập trung vào EUV 0.33-NA, TSMC có thể sử dụng các kỹ thuật multi-patterning để duy trì cùng mức độ phức tạp trong thiết kế mà không cần độ chính xác cực cao của High-NA EUV, cuối cùng giữ chi phí sản xuất ở mức thấp hơn.

Điều thú vị là, quyết định bỏ qua High-NA EUV của TSMC thực sự đặt công ty này phía sau các đối thủ như Intel Foundry trong việc áp dụng các công cụ mới nhất, vì Intel được cho là sẽ sử dụng High-NA cho quy trình 18A dự kiến ra mắt ngay trong năm tới. Với mục tiêu A14P vào năm 2029, TSMC sẽ chậm trễ ít nhất 4 năm trong việc áp dụng High-NA so với các đối thủ cạnh tranh, đây có thể là một quyết định mang lại lợi thế cho các đối thủ.

Trong nhiều năm, TSMC luôn là nhà tiên phong và thường là người tạo ra xu hướng trong việc áp dụng các yếu tố mới trong ngành bán dẫn. Nhưng giờ đây, có vẻ như công ty sẽ bỏ qua việc sử dụng công cụ quang khắc High-NA EUV cho quy trình A14 của mình, mà sẽ dựa vào công nghệ EUV 0.33-NA thông thường hơn. Thông tin này được tiết lộ tại Hội nghị chuyên đề Công nghệ Bắc Mỹ (NA Technology Symposium), nơi Phó Chủ tịch Cấp cao (SVP) của TSMC, Kevin Zhang, đã công bố về sự phát triển này (thông qua Bits & Chips). Với điều này, có thể nói rằng Intel Foundry và một số nhà sản xuất DRAM hiện đang có lợi thế 'công nghệ' hơn so với TSMC.

Phát biểu của ông Kevin Zhang tại sự kiện:

"TSMC sẽ không sử dụng quang khắc High-NA EUV để tạo mẫu chip A14, việc sản xuất dự kiến bắt đầu vào năm 2028. Từ 2 nanomet đến A14, chúng tôi không cần phải sử dụng High-NA, mà vẫn có thể duy trì độ phức tạp tương tự về các bước xử lý."

"Ở mỗi thế hệ công nghệ, chúng tôi cố gắng giảm thiểu số lượng mặt nạ (mask) tăng thêm. Điều này rất quan trọng để cung cấp một giải pháp hiệu quả về chi phí."

Vâng, lý do chính khiến TSMC coi High-NA là không quá cần thiết cho quy trình A14 là vì với các công cụ quang khắc liên quan, gã khổng lồ Đài Loan có thể phải đối mặt với chi phí tăng gấp 2,5 lần so với các phương pháp EUV truyền thống, và điều này cuối cùng sẽ làm cho nút A14 trở nên đắt đỏ hơn nhiều trong sản xuất, đồng nghĩa với việc việc áp dụng nó vào các sản phẩm tiêu dùng sẽ trở nên khó khăn. Gã khổng lồ Đài Loan đang dựa vào thiết kế và khả năng của chip hiện tại, nhưng điều này chắc chắn không có nghĩa là công ty sẽ không sử dụng High-NA EUV cho các quy trình trong tương lai, vì họ có kế hoạch sử dụng nó cho nút A14P.

Một trong những lý do khác khiến High-NA đẩy chi phí lên cao là node A14 của TSMC sẽ yêu cầu nhiều mặt nạ cho một lớp thiết kế chip duy nhất hơn, việc sử dụng các công cụ quang khắc mới nhất đơn giản có nghĩa là gã khổng lồ Đài Loan đang làm tăng chi phí mà không thu được nhiều lợi ích. Thay vào đó, bằng cách tập trung vào EUV 0.33-NA, TSMC có thể sử dụng các kỹ thuật multi-patterning để duy trì cùng mức độ phức tạp trong thiết kế mà không cần độ chính xác cực cao của High-NA EUV, cuối cùng giữ chi phí sản xuất ở mức thấp hơn.

Điều thú vị là, quyết định bỏ qua High-NA EUV của TSMC thực sự đặt công ty này phía sau các đối thủ như Intel Foundry trong việc áp dụng các công cụ mới nhất, vì Intel được cho là sẽ sử dụng High-NA cho quy trình 18A dự kiến ra mắt ngay trong năm tới. Với mục tiêu A14P vào năm 2029, TSMC sẽ chậm trễ ít nhất 4 năm trong việc áp dụng High-NA so với các đối thủ cạnh tranh, đây có thể là một quyết định mang lại lợi thế cho các đối thủ.