Hoàng Đức

Writer

Khi năm 2025 sắp kết thúc, "Mười dự đoán về xu hướng công nghệ bán dẫn hàng đầu" đã thống trị các tiêu đề báo chí vào đầu năm cũng sắp được công bố. Các lĩnh vực cốt lõi như 2nm, HBM4, công nghệ đóng gói tiên tiến, bộ xử lý AI, chip lái xe tự động và bộ xử lý lượng tử luôn là tâm điểm chú ý của ngành công nghiệp. Những dự đoán này đã tiến triển đến đâu trong năm nay? Hôm nay, chúng ta hãy cùng phân tích sự tiến triển thực tế của mười xu hướng này theo một dòng thời gian.

Trong số 10 dự đoán hàng đầu về chất bán dẫn, có bao nhiêu dự đoán đã trở thành sự thật?

2nm: Từ "Ai có thể đạt được sản xuất hàng loạt trước tiên" đến "Ai có thể cung cấp ổn định"

Đầu năm nay, nhiều người dự đoán rằng năm 2025 sẽ là "năm đầu tiên sản xuất hàng loạt" công nghệ xử lý 2nm. Giờ đây, có vẻ như mục tiêu này về cơ bản đã đạt được, nhưng cần phải gọi đó là một "giai đoạn".

Các dự đoán trước đó cho thấy TSMC, Samsung và Intel đều có kế hoạch ra mắt quy trình sản xuất 2nm hoặc tương đương (như Intel 18A) vào năm 2025.Hiện tại, TSMC đã bắt đầu nhận đơn đặt hàng trước cho quy trình sản xuất 2nm của mình vào tháng 4 năm nay, với kế hoạch sản xuất hàng loạt vào cuối quý 4. Khách hàng bao gồm các nhà sản xuất chip hàng đầu như Apple, Nvidia, AMD, Qualcomm và MediaTek.

Chủ tịch TSMC, ông C.C. Wei, cho biết nhu cầu về chip 2nm đã vượt qua nhu cầu về chip thế hệ 3nm. Để đáp ứng nhu cầu đặt hàng ngày càng tăng, TSMC đang lên kế hoạch mở rộng năng lực sản xuất. Đến nay, TSMC đã lên kế hoạch xây dựng tổng cộng bảy nhà máy sản xuất wafer 2nm, đặt tại Khu công nghệ Hsinchu (2 nhà máy) và Khu công nghệ Kaohsiung Nanzih (5 nhà máy). Nếu ba nhà máy bổ sung được hoàn thành thành công, tổng số nhà máy sản xuất wafer 2nm chuyên dụng sẽ tăng lên 10.

Bộ vi xử lý ứng dụng di động 2nm đầu tiên của Samsung Electronics, Exynos 2600, đã chính thức đi vào sản xuất hàng loạt, với tỷ lệ sản phẩm đạt chuẩn hiện tại ổn định ở mức 50%-60%. Tuy nhiên, tin tức này chưa tạo ra phản ứng đáng kể trên thị trường. Lý do cốt lõi có thể nằm ở sự không chắc chắn xung quanh tỷ lệ sản phẩm đạt chuẩn của quy trình 2nm, cùng với các vấn đề về triển khai kỹ thuật và kiểm soát chi phí đã từng bộc lộ trong giai đoạn sản xuất hàng loạt quy trình 3nm. Điều này đã khiến ngành công nghiệp duy trì thái độ chờ đợi và quan sát đối với khả năng cung ứng quy mô lớn và tính cạnh tranh trên thị trường của con chip chủ lực này.

Quy trình sản xuất 18A của Intel đã được đưa vào sản xuất hàng loạt tại nhà máy Fab 52 ở Arizona. Quy trình này sử dụng công nghệ bóng bán dẫn cổng toàn diện và công nghệ nguồn điện phía sau, đạt được những cải tiến về hiệu quả năng lượng và mật độ.

Cần lưu ý rằng "sản xuất hàng loạt" không đồng nghĩa với "cung cấp quy mô lớn". Hiện tại, năng lực sản xuất 2nm còn rất hạn chế, chủ yếu phục vụ các khách hàng có lợi nhuận cao, và việc ứng dụng rộng rãi trong các sản phẩm tiêu dùng còn ít nhất một năm rưỡi nữa mới diễn ra. Sản xuất hàng loạt thực sự dự kiến sẽ không diễn ra cho đến năm 2026.

HBM4, SK Hynix một lần nữa dẫn đầu.

Nếu năm 2024 là năm bùng nổ của HBM3E, thì năm 2025 chắc chắn sẽ là năm HBM4 cất cánh.

Vào tháng 9 năm nay, SK Hynix đã hoàn thành việc phát triển chip nhớ HBM4 và bước vào giai đoạn sản xuất hàng loạt, sáu tháng sau khi cung cấp các mẫu HBM4 12 lớp cho các khách hàng lớn như Nvidia . Các sản phẩm HBM4 của hãng sẽ bắt đầu được xuất xưởng vào quý IV năm nay, với kế hoạch mở rộng doanh số bán hàng hoàn toàn vào năm tới.

Các cuộc đàm phán giữa Samsung Electronics và Nvidia về giá cung cấp HBM4 đã bước vào giai đoạn cuối. Samsung đang tránh một sai lầm có thể dẫn đến mất vị thế thống trị trên thị trường DRAM và đang tận dụng việc sản xuất hàng loạt HBM4 dựa trên công nghệ DRAM 1c tiên tiến hơn của mình để đảm bảo lợi thế cạnh tranh so với HBM4 dựa trên công nghệ DRAM 1b của SK Hynix. Tuy nhiên, các sản phẩm HBM4 của Samsung hiện vẫn đang trong giai đoạn thử nghiệm cuối cùng, và các chuyên gia trong ngành dự đoán rằng việc vận chuyển hàng loạt có thể sẽ không bắt đầu cho đến năm 2026.

Bao bì cao cấp, nhiều điểm nhấn là những bông hoa đỏ.

Công nghệ đóng gói tiên tiến đã trở thành con đường cốt lõi để tiếp tục duy trì Định luật Moore. Năm 2025 không chỉ là một năm quan trọng đối với việc ra mắt năng lực sản xuất CoWoS, mà còn là một cột mốc then chốt trong việc triển khai công nghệ quang học đóng gói đồng thời thế hệ tiếp theo (CoPoS).

TSMC đã đưa nhà máy AP8 của Innolux tại Khu Công nghệ Nam Đài Loan vào hoạt động như cơ sở sản xuất chính cho CoWoS-L, và nhà máy này đã đạt công suất hoạt động tối đa trong nửa cuối năm nay. Các nhà máy ở Zhunan và Longtan cũng đang điều chỉnh công suất sản xuất để đáp ứng sự tăng trưởng nhu cầu trong tương lai đối với các công nghệ như CoWoS-L và InFO-M.

Điều đáng chú ý là trong khi TSMC tiếp tục mở rộng năng lực sản xuất CoWoS, công ty cũng đang đẩy nhanh nghiên cứu và phát triển công nghệ CoPoS và xây dựng các cơ sở sản xuất. Công ty đã công bố danh sách nhà cung cấp và thông số kỹ thuật thiết bị đợt đầu tiên sớm hơn dự kiến vào quý 3 năm 2025. TSMC dự kiến sẽ thiết lập dây chuyền sản xuất thí điểm CoPoS đầu tiên tại VisEra vào năm 2026, và sản xuất hàng loạt sẽ diễn ra tại nhà máy Chiayi AP7.

Các nhà phân tích của Morgan Stanley mới đây đã công bố một báo cáo dự đoán rằng công suất sản xuất CoWoS hàng tháng của TSMC sẽ đạt ít nhất 120.000 đến 130.000 tấm wafer vào cuối năm 2026, tăng so với ước tính trước đó là 100.000 tấm wafer. Sự điều chỉnh tăng đáng kể này dựa trên khảo sát ngành mới nhất của ngân hàng.

Trong khi đó, các công ty đóng gói và kiểm thử trong nước cũng đang đẩy nhanh nỗ lực để bắt kịp. Trong nửa đầu năm 2025, cơ sở đóng gói và kiểm thử chip chuyên dụng cho ngành ô tô của Tập đoàn JCET đã hoàn thành và sẽ đi vào sản xuất trong nửa cuối năm. Giai đoạn đầu của dự án của Công ty TNHH Vi điện tử tiên tiến Tongfu (Tô Châu) đã đạt sản xuất hàng loạt vào tháng 1 năm 2025, tập trung vào đóng gói và kiểm thử FCBGA cao cấp. Dự án đóng gói và kiểm thử bo mạch của Công ty TNHH Bán dẫn Giang Tô Pangu thuộc Tập đoàn Công nghệ Huatian, nhằm thúc đẩy sản xuất hàng loạt quy mô lớn công nghệ đóng gói fan-out cấp bo mạch, cũng đã bắt đầu sản xuất một phần trong năm nay.

NVIDIA Blackwell Ultra GB300, một sản phẩm đột phá.

Vào tháng 3 năm nay, tại GTC 2025, NVIDIA đã chính thức ra mắt chip Blackwell Ultra GB300 mới, bắt đầu sản xuất hàng loạt vào quý 3. GPU B300 mới sẽ cung cấp thông lượng tính toán cao hơn so với B200, và bộ nhớ trên chip nhiều hơn 50% sẽ hỗ trợ các mô hình AI với tập tham số lớn hơn, đồng thời sức mạnh tính toán tương ứng chắc chắn sẽ được cải thiện. Ngoài ra, NVIDIA cũng đã giới thiệu chip thế hệ tiếp theo của mình, "Rubin", dự kiến sẽ được phát hành vào nửa cuối năm 2026. Chip Rubin sẽ đưa hiệu năng lên một tầm cao mới, với hiệu năng suy luận FP4 lên đến 50 petaflops, hơn gấp đôi so với chip Blackwell hiện tại.

Vào tháng 6 năm nay, AMD đã công bố kiến trúc GPU CDNA 4 mới tại hội nghị ADVANCING AI 2025, ra mắt dòng GPU AMD Instinct MI350 và ROCm 7 mới. Là card tăng tốc AI đầu tiên áp dụng kiến trúc CDNA 4, dòng GPU Instinct MI350 bao gồm Instinct MI350X với TDP tối đa 1000W, được thiết kế cho hệ thống làm mát bằng không khí, và Instinct MI355X với TDP tối đa 1400W và hiệu năng mạnh mẽ hơn, được thiết kế cho hệ thống làm mát bằng chất lỏng. Ngoài dòng GPU Instinct MI350 mới, AMD cũng giới thiệu trước dòng GPU MI400, dự kiến ra mắt vào năm 2026, hứa hẹn mở ra kỷ nguyên mới cho GPU điện toán hiệu năng cao dành cho AI.

Intel thông báo sẽ ra mắt bộ vi xử lý Core Ultra thế hệ thứ ba "Panther Lake" trên toàn cầu tại CES 2026.

Bên cạnh việc liên tục ra mắt các chip AI mới, một thay đổi đáng kể khác trong năm 2025 là sự đa dạng hóa của thị trường bộ xử lý AI, với nhóm ASIC, đại diện bởi Google, đạt được những bước tiến đột phá trong năm đó.

Dữ liệu thử nghiệm thực tế cho thấy rằng khi xử lý các mô hình AI cụ thể, tốc độ tính toán của TPU có thể đạt gấp 1,5-2 lần so với GPU NVIDIA cùng thế hệ, với hiệu quả năng lượng được cải thiện khoảng 30%. Lợi thế về hiệu năng này xuất phát từ triết lý thiết kế "tích hợp phần cứng-phần mềm" của Google - TPU được tối ưu hóa đặc biệt cho khung TensorFlow, với khả năng tùy chỉnh sâu rộng từ kiến trúc chip đến trình biên dịch. Tuy nhiên, NVIDIA tự tin vào tính linh hoạt của GPU của mình. Chip A100 không chỉ hỗ trợ tất cả các khung AI phổ biến mà còn có thể xử lý nhiều tác vụ như kết xuất đồ họa và tính toán khoa học.

Các chip chuyên dụng cho ô tô sản xuất Trung Quốc đang được ứng dụng rộng rãi trong xe hơi.

Năm 2025 cũng được nhiều nhà sản xuất chip dành cho ô tô xem là giai đoạn cuối cùng cho công nghệ lái xe thông minh cao cấp và là cơ hội để sản xuất hàng loạt và ứng dụng vào xe hơi.

Ngày 22/11, Horizon Robotics thông báo rằng giải pháp lái xe thông minh tiên tiến của họ, HSD (Horizon SuperDrive), đã giành được hợp đồng với 10 nhà sản xuất ô tô trong và ngoài nước cho hơn 20 mẫu xe. Được trang bị chip Journey 6P với sức mạnh tính toán tối đa 560 TOPS, giải pháp này có thể triển khai các mô hình quy mô lớn như end-to-end, VLA và VLM. Hơn nữa, dòng chip Journey của hãng đã vượt mốc 10 triệu đơn vị sản xuất hàng loạt và xuất xưởng, trở thành công ty trong nước đầu tiên xuất xưởng hơn 10 triệu chip lái xe thông minh.

Robot Journey 6P sử dụng kiến trúc đa lõi không đồng nhất, cung cấp sức mạnh tính toán để hỗ trợ việc triển khai nhanh chóng các hệ thống hỗ trợ lái xe tiên tiến (HSD). Horizon Robotics cho biết giải pháp HSD của họ bao gồm các tình huống trên đường cao tốc, đô thị và bãi đậu xe, và đã bắt đầu hợp tác sản xuất hàng loạt với các nhà sản xuất ô tô hàng đầu quốc tế, dự kiến việc triển khai sẽ bắt đầu dần dần từ năm 2026.

Dòng chip điện toán đa lĩnh vực thông minh Wudang C1200 của Black Sesame Technologies được ra mắt vào tháng 4/ 2023. Đây là nền tảng SoC điện toán đa lĩnh vực đầu tiên trong ngành được thiết kế dành cho xe thông minh, đáp ứng các yêu cầu cao nhất về an toàn và độ tin cậy cấp ô tô. Trong đó, chip C1236 hướng đến khả năng lái xe thông minh tiên tiến, hỗ trợ tích hợp NOA (Tiếng ồn, Đến nơi và Chế độ lái tự động) trên một chip duy nhất; chip C1296 hỗ trợ hợp nhất đa lĩnh vực trên một chip duy nhất. Dựa trên dòng sản phẩm C1200, Black Sesame Technologies đã hợp tác với nhiều khách hàng, bao gồm các nhà sản xuất thiết bị gốc (OEM) và các đối tác trong hệ sinh thái như FAW Hongqi, Wind River, Junlian Intelligent và Banma Zhixing.

Vào tháng 3 năm nay, ChipEngine đã chính thức ra mắt chip lái xe tự hành cao cấp "Star One" 7nm dành cho mọi tình huống, cùng với các giải pháp buồng lái thông minh và lái xe thông minh tương ứng. Chip này dự kiến sẽ được triển khai rộng rãi trong các phương tiện vào năm tới. Chip này sử dụng quy trình sản xuất 7nm đạt chuẩn ô tô, tuân thủ tiêu chuẩn AEC-Q100 và tích hợp kiến trúc đa lõi không đồng nhất để tăng cường sức mạnh tính toán cho việc lái xe thông minh. Sức mạnh tính toán của CPU đạt 250 KDMIPS, và sức mạnh tính toán của NPU đạt 512 TOPS, đạt công suất tính toán tối đa 2048 TOPS thông qua sự hợp tác đa chip.

Bộ xử lý lượng tử vẫn đang trong giai đoạn xây dựng cơ sở.

Đầu năm nay, một số người tin rằng "bộ xử lý lượng tử sẽ bước vào giai đoạn khám phá ứng dụng thực tiễn vào năm 2025". Nhìn lại bây giờ, nhận định này về cơ bản là đúng, nhưng vẫn còn quá sớm để nói rằng chúng đã "có tính ứng dụng thực tiễn".

Gần đây, gã khổng lồ công nghệ IBM đã cho ra mắt hai chip lượng tử thử nghiệm – Loon và Nighthawk. Tuy nhiên, theo lộ trình được sửa đổi gần đây, IBM đã vạch ra một lộ trình từ năm 2025 đến năm 2033 và xa hơn nữa. Lộ trình cho thấy Kookaburra, được đề cập trong dự báo trước đó, sẽ được ra mắt vào năm 2026. Đây sẽ là mô-đun bộ xử lý lượng tử đầu tiên có khả năng lưu trữ thông tin trong bộ nhớ qLDPC và xử lý nó thông qua một LPU bổ sung, mở rộng các hệ thống chịu lỗi vượt ra ngoài một chip đơn lẻ.

Vào năm 2027, Cockatoo sẽ sử dụng bộ ghép L để tạo ra sự vướng víu lượng tử giữa hai mô-đun Kookaburra, từ đó kết nối các chip lượng tử với nhau như các nút trong một hệ thống lớn, tránh được việc phải chế tạo các chip lớn không thực tế. Vào năm 2029, họ sẽ cho ra mắt máy tính lượng tử chịu lỗi quy mô lớn đầu tiên trên thế giới - IBM Quantum Starling.

Những thành tựu này có ý nghĩa khoa học to lớn, chứng minh tính khả thi của điện toán lượng tử chịu lỗi, nhưng vẫn còn một thời gian dài nữa trước khi chúng sẵn sàng cho ứng dụng hoàn thiện. Bộ xử lý lượng tử vẫn là "công nghệ của tương lai", và những tiến bộ trong năm 2025 chủ yếu là "đặt nền móng" hơn là "xây dựng ngôi nhà".

Công nghệ quang tử silicon và CPO: Kỷ nguyên 1.6T lặng lẽ bắt đầu

Khi các cụm AI tiến gần đến giới hạn về băng thông và mức tiêu thụ điện năng, việc tích hợp quang tử silicon và quang học đóng gói chung (CPO) đã trở thành những lựa chọn phổ biến.

Vào năm 2025, Broadcom, Cisco và Ayar Labs đã cùng nhau quảng bá công nghệ CPO, giúp giảm đáng kể mức tiêu thụ điện năng trong quá trình chuyển đổi từ 800G lên 1.6T. Meta và Microsoft đã thử nghiệm các thiết bị chuyển mạch CPO trong một số cụm AI để xác minh độ tin cậy của chúng.

TSMC đã kết hợp thành công công nghệ quang học đóng gói đồng thời (CPO) với công nghệ đóng gói bán dẫn tiên tiến. Dự kiến các mẫu thử nghiệm sẽ bắt đầu vào đầu năm 2025, một thành tựu báo hiệu sự gia nhập của TSMC vào kỷ nguyên truyền dẫn quang 1.6T trong cùng năm đó. Các dự báo trong ngành cho thấy Broadcom và Nvidia có khả năng nằm trong số những người dùng đầu tiên của giải pháp TSMC.

LightCounting dự đoán rằng lượng xuất xưởng toàn cầu của các mô-đun quang 800G sẽ vượt quá 5 triệu đơn vị vào năm 2025, với các giải pháp LPO dự kiến chiếm hơn 40%, so với con số dưới 500.000 đơn vị vào năm 2023. Các mô-đun quang 800G, đặc biệt là những mô-đun sử dụng công nghệ LPO, đang trong giai đoạn phát triển nhanh chóng, đóng vai trò ngày càng quan trọng trong kỷ nguyên bùng nổ sức mạnh tính toán AI và liên tục thúc đẩy sự định hình lại và chuyển đổi của bối cảnh kết nối quang học trung tâm dữ liệu.

Tiếp nối mô-đun quang 800G, khi các cụm máy chủ AI đặt ra yêu cầu cao hơn về tốc độ kết nối, NVIDIA đã chọn chuyển sang sử dụng mô-đun quang 1.6T trong các máy chủ GB300 của mình, đồng thời cung cấp tùy chọn nâng cấp lên mô-đun quang 1.6T trong các máy chủ GB200. Như vậy, mô-đun quang 1.6T đang dần trở nên phổ biến.

Về dự báo phát triển trong tương lai, tốc độ sẽ đạt 1,6T trong vòng 1-2 năm tới. Dự kiến đến năm 2029, tốc độ mô-đun quang học cho các ứng dụng AI sẽ đạt 3,2T, và đến năm 2030, tốc độ 3,2T sẽ được sử dụng rộng rãi.

Bước vào chiến trường cốt lõi của điện toán AI

Đến năm 2025, RISC-V sẽ không còn chỉ là từ đồng nghĩa với "MCU tiết kiệm năng lượng" mà sẽ chính thức tham gia vào lĩnh vực điện toán trí tuệ nhân tạo.

Trên thực tế, ngay từ năm 2024, bộ xử lý RISC-V hiệu năng cao mã nguồn mở thế hệ thứ ba "Xiangshan" do Viện Công nghệ Máy tính thuộc Viện Hàn lâm Khoa học Trung Quốc và Viện Nghiên cứu Chip Mã nguồn Mở Bắc Kinh phát hành đã lọt vào nhóm hàng đầu về hiệu năng. Ngoài ra, một số công ty trong nước như Nuclei Technology, Easiway và Jinze Technology đã phát hành IP, bộ công cụ, nền tảng phần mềm, chip PC AI, MCU AI, bộ xử lý đa phương tiện và các chip khác, cũng như bo mạch phát triển và các sản phẩm khác.

Xét từ tiến trình hiện tại, RISC-V đang đồng thời tiến vào ba lĩnh vực có giá trị cao: trí tuệ nhân tạo biên (edge AI), xe thông minh và trung tâm dữ liệu. Nó không còn bị giới hạn ở các thiết bị IoT công suất thấp, mà thể hiện khả năng thâm nhập đa cấp: nó có thể được nhúng vào chip đánh thức bằng giọng nói, hỗ trợ hệ thống ra quyết định của xe thông minh, và thậm chí trở thành nền tảng đáng tin cậy của trung tâm dữ liệu đám mây.

Trong quá trình thúc đẩy sự tích hợp sâu rộng giữa RISC-V và AI, các công ty như ESW Computing, China Mobile ChipStar và Advanced Spacetime đều đã có những đóng góp đáng kể. Trong lĩnh vực ô tô, Infineon và Mobileye đã liên tiếp cho ra mắt các giải pháp ADAS. NVIDIA đang tích cực thúc đẩy việc chuyển đổi CUDA sang kiến trúc RISC-V, điều này có nghĩa là các nhà phát triển có thể tự do lựa chọn kiến trúc CPU cho trung tâm dữ liệu, và sẽ thúc đẩy ứng dụng rộng rãi của RISC-V trong lĩnh vực điện toán hiệu năng cao ở cấp độ hệ sinh thái.

RISC-V International dự đoán rằng đến năm 2031, chip RISC-V sẽ chiếm thị phần đáng kể trong sáu thị trường chính: điện tử tiêu dùng (39%), máy tính (33%), ô tô (31%), trung tâm dữ liệu (28%), công nghiệp (27%) và truyền thông mạng (26%), với tổng số lượng xuất xưởng vượt quá 20 tỷ đơn vị.

Màn hình SiC 8 inch bắt đầu sản xuất hàng loạt

Vào năm 2025, ngành công nghiệp silicon carbide sẽ chính thức bước vào giai đoạn chuyển đổi sang sản xuất tấm wafer 8 inch, với các công ty như STMicroelectronics, Coretronic, Rohm, Resonac và ON Semiconductor đều đã đi vào hoạt động các nhà máy sản xuất wafer SiC 8 inch.

Nâng cấp từ tấm wafer silicon carbide 6 inch lên 8 inch làm tăng chi phí xử lý chất nền, nhưng lại giúp tăng năng suất chip. Một tấm wafer 8 inch có thể sản xuất số lượng chip nhiều gấp khoảng 1,8 lần so với tấm wafer silicon carbide 6 inch. Việc chuyển sang sử dụng wafer 8 inch là một cách khả thi để giảm chi phí sản xuất thiết bị silicon carbide. Hơn nữa, độ dày chất nền tăng lên ở wafer 8 inch giúp duy trì hình dạng trong quá trình xử lý, giảm hiện tượng cong vênh cạnh và giảm mật độ khuyết tật, từ đó cải thiện năng suất. Sử dụng chất nền 8 inch có thể giảm đáng kể chi phí đơn vị tổng thể.

Trong số các công ty Trung Quốc, Tianyue Advanced, Tianke Heda và Sanan Optoelectronics đều đã đạt được khả năng sản xuất hàng loạt quy mô lớn. Năng lực sản xuất chất nền của Tianyue Advanced, chủ yếu là tấm wafer 8 inch, đạt 460.000 tấm wafer/năm vào năm 2024, và mục tiêu tổng năng lực sản xuất là tăng lên 600.000 tấm wafer/năm vào năm 2025. Nhà máy Lingang, Thượng Hải của công ty đã đạt năng lực sản xuất hàng năm là 300.000 chất nền dẫn điện vào giữa năm 2024 và hiện đang thúc đẩy giai đoạn mở rộng năng lực sản xuất thứ hai. Các cơ sở Jinan và Jining đã hình thành chuỗi cung ứng hợp tác với cơ sở Lingang.

Năm 2024, Tianke Heda đã đạt được sản xuất hàng loạt chất nền 8 inch. Đến năm 2025, tổng công suất sản xuất chất nền dự kiến đạt từ 500.000 đến 800.000 tấm wafer (bao gồm cả wafer 8 inch), và công suất sản xuất wafer epitaxy là 250.000 tấm. Với các cơ sở tại Bắc Kinh và Từ Châu làm nòng cốt, liên doanh Thâm Quyến đã tái đầu tư vào Tianke để tiếp tục tăng cường năng lực sản xuất chất nền 6-8 inch và wafer epitaxy. Hơn nữa, các sản phẩm 8 inch đã được các nhà sản xuất thiết bị lớn trong và ngoài nước kiểm chứng và đã nhận được các đơn đặt hàng sản xuất hàng loạt LTA trong nhiều năm.

Trong nửa đầu năm 2025, cơ sở tại Hồ Nam của Sanan Optoelectronics có công suất sản xuất đế 8 inch là 1.000 tấm wafer/tháng và công suất sản xuất lớp màng mỏng (epitaxial) là 2.000 tấm wafer/tháng. Cơ sở tại Trùng Khánh, một liên doanh với STMicroelectronics, dự kiến có công suất sản xuất đế 8 inch là 480.000 tấm wafer/năm. Cơ sở này đã được đưa vào hoạt động và cung cấp mẫu để kiểm chứng vào tháng 2 năm 2025.

Tấm silicon carbide 8 inch đang thúc đẩy sự bùng nổ của nhiều kịch bản ứng dụng. Trong lĩnh vực xe điện, nền tảng 800V đã trở thành tiêu chuẩn. Trong lĩnh vực quang điện, các thiết bị silicon carbide có hiệu suất trên 98%, và các giải pháp tích hợp quang điện và lưu trữ năng lượng đã trở thành tiêu chuẩn ngành. Ngoài ra, tại các thị trường mới nổi, chất nền 8 inch có thể sản xuất 3-4 cặp kính AR, và việc giảm chi phí sẽ đẩy nhanh sự phát triển của kính AR và các ứng dụng khác.

Trí tuệ nhân tạo + Phân tích dữ liệu khám phá (EDA): Tầm quan trọng của nó ngày càng nổi bật

Đến năm 2025, trí tuệ nhân tạo (AI) sẽ không chỉ còn là "công cụ tăng tốc" trong quy trình thiết kế mạch điện tử (EDA), mà sẽ bắt đầu định hình lại mô hình thiết kế chip.

Phần mềm DSO.ai của Synopsys được sử dụng rộng rãi trong thiết kế các nút công nghệ dưới 2nm. Nó có thể tự động tìm kiếm phương án bố trí và định tuyến tối ưu mà không cần can thiệp thủ công, đạt được sự cải thiện tổng thể về PPA (hiệu năng, điện năng tiêu thụ, diện tích) hơn 10%.

Công nghệ NVIDIA cuLitho sử dụng các cụm GPU để tăng tốc các phép tính OPC (Hiệu chỉnh khoảng cách quang học), rút ngắn quá trình tạo mặt nạ từ nhiều tuần xuống còn vài giờ, nhanh hơn tới 40 lần.

SemiKong, mô hình lớn mã nguồn mở của Aitomatic, hỗ trợ các quy tắc thiết kế truy vấn ngôn ngữ tự nhiên, tự động tạo các đoạn mã Verilog và hỗ trợ định vị lỗi. Nó đã được một số công ty khởi nghiệp sử dụng để tạo mẫu nhanh.

AI+EDA đang làm giảm rào cản gia nhập thị trường thiết kế chip cao cấp.

Nhìn lại mười dự đoán hàng đầu được đưa ra vào đầu năm, hầu hết các hướng đi đều tiến triển theo kế hoạch, một số bị chậm lại một chút, và một số thậm chí còn vượt quá mong đợi. Đứng trước ngưỡng cửa năm 2025 và hướng tới năm 2026, bước đột phá công nghệ tiếp theo có thể không còn xa nữa, nó nằm trong những nhà máy sản xuất chip đang âm thầm mở rộng sản xuất, trong nhật ký về việc tăng năng suất và trong từng dòng mã được các kỹ sư gõ ra.

Trong số 10 dự đoán hàng đầu về chất bán dẫn, có bao nhiêu dự đoán đã trở thành sự thật?

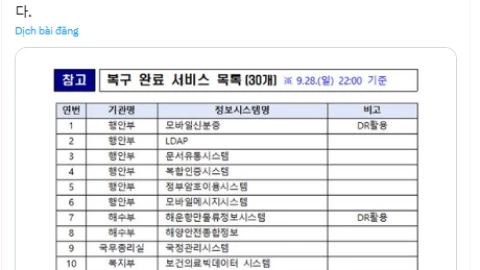

| Lĩnh vực | Dự đoán đầu năm | Tiến độ đạt được |

|---|---|---|

| 2nm | TSMC, Samsung, Intel lần lượt ra quy trình 2nm / Intel 18A trong năm | TSMC dự kiến sản xuất thử cuối năm; Samsung & Intel đã sản xuất nhưng tỷ lệ khác nhau |

| HBM4 | SK Hynix & Samsung dự kiến sản xuất hàng loạt trong năm | SK Hynix đã sản xuất HBM4, xuất hàng từ Q4; Samsung lùi sang 2026 |

| Đóng gói tiên tiến | TSMC mở rộng CoWoS, tăng kích thước reticle; doanh nghiệp nội địa đầu tư nhà máy | CoWoS tiếp tục sản xuất ổn định; tiến độ xây dựng nhà máy trong nước thuận lợi |

| Chip AI | Intel: Panther Lake, Clearwater Forest; NVIDIA: Blackwell Ultra GB300; AMD: CDNA 4 | NVIDIA đã ra GB300 & CDNA 4; Panther Lake (Ultra Gen 3) ra mắt tại CES 2026 |

| Chip ô tô | Horizon, Black Sesame… có chip sản xuất / lên xe; GPU rời ô tô của Intel ra 2025 | Horizon HSD được >10 hãng xe, >20 mẫu; Black Sesame C1200E hợp tác nhiều khách hàng |

| Máy tính lượng tử | IBM ra CPU lượng tử 1386 qubit – Kookaburra | IBM ra chip thử nghiệm Loon & Nighthawk; Kookaburra dời sang 2026 |

| Chip quang (Silicon Photonics) | Công nghệ dần chín muồi; TSMC đạt nguồn sáng 1.6T cho mô-đun cắm rời (2025) | Broadcom, Ayar Labs thúc đẩy CPO; TSMC kết hợp CPO + đóng gói tiên tiến |

| AI + EDA | AI hỗ trợ / thay thế thuật toán mô phỏng EDA | Synopsys DSO.ai dùng cho thiết kế <2nm; NVIDIA cuLitho tăng tốc OPC |

| RISC-V | Tiếp tục thâm nhập chip hiệu năng cao | Bước vào tính toán AI, dùng cho AI biên, ô tô, trung tâm dữ liệu (Tenstorrent, SiFive, Intel, Mobileye…) |

| SiC | Đẩy nhanh chuyển từ wafer 6 inch → 8 inch | Infineon, Wolfspeed, Rohm… có 8-inch SiC; Trung Quốc đã có sản xuất quy mô lớn |

Đầu năm nay, nhiều người dự đoán rằng năm 2025 sẽ là "năm đầu tiên sản xuất hàng loạt" công nghệ xử lý 2nm. Giờ đây, có vẻ như mục tiêu này về cơ bản đã đạt được, nhưng cần phải gọi đó là một "giai đoạn".

Các dự đoán trước đó cho thấy TSMC, Samsung và Intel đều có kế hoạch ra mắt quy trình sản xuất 2nm hoặc tương đương (như Intel 18A) vào năm 2025.Hiện tại, TSMC đã bắt đầu nhận đơn đặt hàng trước cho quy trình sản xuất 2nm của mình vào tháng 4 năm nay, với kế hoạch sản xuất hàng loạt vào cuối quý 4. Khách hàng bao gồm các nhà sản xuất chip hàng đầu như Apple, Nvidia, AMD, Qualcomm và MediaTek.

Chủ tịch TSMC, ông C.C. Wei, cho biết nhu cầu về chip 2nm đã vượt qua nhu cầu về chip thế hệ 3nm. Để đáp ứng nhu cầu đặt hàng ngày càng tăng, TSMC đang lên kế hoạch mở rộng năng lực sản xuất. Đến nay, TSMC đã lên kế hoạch xây dựng tổng cộng bảy nhà máy sản xuất wafer 2nm, đặt tại Khu công nghệ Hsinchu (2 nhà máy) và Khu công nghệ Kaohsiung Nanzih (5 nhà máy). Nếu ba nhà máy bổ sung được hoàn thành thành công, tổng số nhà máy sản xuất wafer 2nm chuyên dụng sẽ tăng lên 10.

Bộ vi xử lý ứng dụng di động 2nm đầu tiên của Samsung Electronics, Exynos 2600, đã chính thức đi vào sản xuất hàng loạt, với tỷ lệ sản phẩm đạt chuẩn hiện tại ổn định ở mức 50%-60%. Tuy nhiên, tin tức này chưa tạo ra phản ứng đáng kể trên thị trường. Lý do cốt lõi có thể nằm ở sự không chắc chắn xung quanh tỷ lệ sản phẩm đạt chuẩn của quy trình 2nm, cùng với các vấn đề về triển khai kỹ thuật và kiểm soát chi phí đã từng bộc lộ trong giai đoạn sản xuất hàng loạt quy trình 3nm. Điều này đã khiến ngành công nghiệp duy trì thái độ chờ đợi và quan sát đối với khả năng cung ứng quy mô lớn và tính cạnh tranh trên thị trường của con chip chủ lực này.

Quy trình sản xuất 18A của Intel đã được đưa vào sản xuất hàng loạt tại nhà máy Fab 52 ở Arizona. Quy trình này sử dụng công nghệ bóng bán dẫn cổng toàn diện và công nghệ nguồn điện phía sau, đạt được những cải tiến về hiệu quả năng lượng và mật độ.

Cần lưu ý rằng "sản xuất hàng loạt" không đồng nghĩa với "cung cấp quy mô lớn". Hiện tại, năng lực sản xuất 2nm còn rất hạn chế, chủ yếu phục vụ các khách hàng có lợi nhuận cao, và việc ứng dụng rộng rãi trong các sản phẩm tiêu dùng còn ít nhất một năm rưỡi nữa mới diễn ra. Sản xuất hàng loạt thực sự dự kiến sẽ không diễn ra cho đến năm 2026.

HBM4, SK Hynix một lần nữa dẫn đầu.

Nếu năm 2024 là năm bùng nổ của HBM3E, thì năm 2025 chắc chắn sẽ là năm HBM4 cất cánh.

Vào tháng 9 năm nay, SK Hynix đã hoàn thành việc phát triển chip nhớ HBM4 và bước vào giai đoạn sản xuất hàng loạt, sáu tháng sau khi cung cấp các mẫu HBM4 12 lớp cho các khách hàng lớn như Nvidia . Các sản phẩm HBM4 của hãng sẽ bắt đầu được xuất xưởng vào quý IV năm nay, với kế hoạch mở rộng doanh số bán hàng hoàn toàn vào năm tới.

Các cuộc đàm phán giữa Samsung Electronics và Nvidia về giá cung cấp HBM4 đã bước vào giai đoạn cuối. Samsung đang tránh một sai lầm có thể dẫn đến mất vị thế thống trị trên thị trường DRAM và đang tận dụng việc sản xuất hàng loạt HBM4 dựa trên công nghệ DRAM 1c tiên tiến hơn của mình để đảm bảo lợi thế cạnh tranh so với HBM4 dựa trên công nghệ DRAM 1b của SK Hynix. Tuy nhiên, các sản phẩm HBM4 của Samsung hiện vẫn đang trong giai đoạn thử nghiệm cuối cùng, và các chuyên gia trong ngành dự đoán rằng việc vận chuyển hàng loạt có thể sẽ không bắt đầu cho đến năm 2026.

Bao bì cao cấp, nhiều điểm nhấn là những bông hoa đỏ.

Công nghệ đóng gói tiên tiến đã trở thành con đường cốt lõi để tiếp tục duy trì Định luật Moore. Năm 2025 không chỉ là một năm quan trọng đối với việc ra mắt năng lực sản xuất CoWoS, mà còn là một cột mốc then chốt trong việc triển khai công nghệ quang học đóng gói đồng thời thế hệ tiếp theo (CoPoS).

TSMC đã đưa nhà máy AP8 của Innolux tại Khu Công nghệ Nam Đài Loan vào hoạt động như cơ sở sản xuất chính cho CoWoS-L, và nhà máy này đã đạt công suất hoạt động tối đa trong nửa cuối năm nay. Các nhà máy ở Zhunan và Longtan cũng đang điều chỉnh công suất sản xuất để đáp ứng sự tăng trưởng nhu cầu trong tương lai đối với các công nghệ như CoWoS-L và InFO-M.

Điều đáng chú ý là trong khi TSMC tiếp tục mở rộng năng lực sản xuất CoWoS, công ty cũng đang đẩy nhanh nghiên cứu và phát triển công nghệ CoPoS và xây dựng các cơ sở sản xuất. Công ty đã công bố danh sách nhà cung cấp và thông số kỹ thuật thiết bị đợt đầu tiên sớm hơn dự kiến vào quý 3 năm 2025. TSMC dự kiến sẽ thiết lập dây chuyền sản xuất thí điểm CoPoS đầu tiên tại VisEra vào năm 2026, và sản xuất hàng loạt sẽ diễn ra tại nhà máy Chiayi AP7.

Các nhà phân tích của Morgan Stanley mới đây đã công bố một báo cáo dự đoán rằng công suất sản xuất CoWoS hàng tháng của TSMC sẽ đạt ít nhất 120.000 đến 130.000 tấm wafer vào cuối năm 2026, tăng so với ước tính trước đó là 100.000 tấm wafer. Sự điều chỉnh tăng đáng kể này dựa trên khảo sát ngành mới nhất của ngân hàng.

Trong khi đó, các công ty đóng gói và kiểm thử trong nước cũng đang đẩy nhanh nỗ lực để bắt kịp. Trong nửa đầu năm 2025, cơ sở đóng gói và kiểm thử chip chuyên dụng cho ngành ô tô của Tập đoàn JCET đã hoàn thành và sẽ đi vào sản xuất trong nửa cuối năm. Giai đoạn đầu của dự án của Công ty TNHH Vi điện tử tiên tiến Tongfu (Tô Châu) đã đạt sản xuất hàng loạt vào tháng 1 năm 2025, tập trung vào đóng gói và kiểm thử FCBGA cao cấp. Dự án đóng gói và kiểm thử bo mạch của Công ty TNHH Bán dẫn Giang Tô Pangu thuộc Tập đoàn Công nghệ Huatian, nhằm thúc đẩy sản xuất hàng loạt quy mô lớn công nghệ đóng gói fan-out cấp bo mạch, cũng đã bắt đầu sản xuất một phần trong năm nay.

NVIDIA Blackwell Ultra GB300, một sản phẩm đột phá.

Vào tháng 3 năm nay, tại GTC 2025, NVIDIA đã chính thức ra mắt chip Blackwell Ultra GB300 mới, bắt đầu sản xuất hàng loạt vào quý 3. GPU B300 mới sẽ cung cấp thông lượng tính toán cao hơn so với B200, và bộ nhớ trên chip nhiều hơn 50% sẽ hỗ trợ các mô hình AI với tập tham số lớn hơn, đồng thời sức mạnh tính toán tương ứng chắc chắn sẽ được cải thiện. Ngoài ra, NVIDIA cũng đã giới thiệu chip thế hệ tiếp theo của mình, "Rubin", dự kiến sẽ được phát hành vào nửa cuối năm 2026. Chip Rubin sẽ đưa hiệu năng lên một tầm cao mới, với hiệu năng suy luận FP4 lên đến 50 petaflops, hơn gấp đôi so với chip Blackwell hiện tại.

Vào tháng 6 năm nay, AMD đã công bố kiến trúc GPU CDNA 4 mới tại hội nghị ADVANCING AI 2025, ra mắt dòng GPU AMD Instinct MI350 và ROCm 7 mới. Là card tăng tốc AI đầu tiên áp dụng kiến trúc CDNA 4, dòng GPU Instinct MI350 bao gồm Instinct MI350X với TDP tối đa 1000W, được thiết kế cho hệ thống làm mát bằng không khí, và Instinct MI355X với TDP tối đa 1400W và hiệu năng mạnh mẽ hơn, được thiết kế cho hệ thống làm mát bằng chất lỏng. Ngoài dòng GPU Instinct MI350 mới, AMD cũng giới thiệu trước dòng GPU MI400, dự kiến ra mắt vào năm 2026, hứa hẹn mở ra kỷ nguyên mới cho GPU điện toán hiệu năng cao dành cho AI.

Intel thông báo sẽ ra mắt bộ vi xử lý Core Ultra thế hệ thứ ba "Panther Lake" trên toàn cầu tại CES 2026.

Bên cạnh việc liên tục ra mắt các chip AI mới, một thay đổi đáng kể khác trong năm 2025 là sự đa dạng hóa của thị trường bộ xử lý AI, với nhóm ASIC, đại diện bởi Google, đạt được những bước tiến đột phá trong năm đó.

Dữ liệu thử nghiệm thực tế cho thấy rằng khi xử lý các mô hình AI cụ thể, tốc độ tính toán của TPU có thể đạt gấp 1,5-2 lần so với GPU NVIDIA cùng thế hệ, với hiệu quả năng lượng được cải thiện khoảng 30%. Lợi thế về hiệu năng này xuất phát từ triết lý thiết kế "tích hợp phần cứng-phần mềm" của Google - TPU được tối ưu hóa đặc biệt cho khung TensorFlow, với khả năng tùy chỉnh sâu rộng từ kiến trúc chip đến trình biên dịch. Tuy nhiên, NVIDIA tự tin vào tính linh hoạt của GPU của mình. Chip A100 không chỉ hỗ trợ tất cả các khung AI phổ biến mà còn có thể xử lý nhiều tác vụ như kết xuất đồ họa và tính toán khoa học.

Các chip chuyên dụng cho ô tô sản xuất Trung Quốc đang được ứng dụng rộng rãi trong xe hơi.

Năm 2025 cũng được nhiều nhà sản xuất chip dành cho ô tô xem là giai đoạn cuối cùng cho công nghệ lái xe thông minh cao cấp và là cơ hội để sản xuất hàng loạt và ứng dụng vào xe hơi.

Ngày 22/11, Horizon Robotics thông báo rằng giải pháp lái xe thông minh tiên tiến của họ, HSD (Horizon SuperDrive), đã giành được hợp đồng với 10 nhà sản xuất ô tô trong và ngoài nước cho hơn 20 mẫu xe. Được trang bị chip Journey 6P với sức mạnh tính toán tối đa 560 TOPS, giải pháp này có thể triển khai các mô hình quy mô lớn như end-to-end, VLA và VLM. Hơn nữa, dòng chip Journey của hãng đã vượt mốc 10 triệu đơn vị sản xuất hàng loạt và xuất xưởng, trở thành công ty trong nước đầu tiên xuất xưởng hơn 10 triệu chip lái xe thông minh.

Robot Journey 6P sử dụng kiến trúc đa lõi không đồng nhất, cung cấp sức mạnh tính toán để hỗ trợ việc triển khai nhanh chóng các hệ thống hỗ trợ lái xe tiên tiến (HSD). Horizon Robotics cho biết giải pháp HSD của họ bao gồm các tình huống trên đường cao tốc, đô thị và bãi đậu xe, và đã bắt đầu hợp tác sản xuất hàng loạt với các nhà sản xuất ô tô hàng đầu quốc tế, dự kiến việc triển khai sẽ bắt đầu dần dần từ năm 2026.

Dòng chip điện toán đa lĩnh vực thông minh Wudang C1200 của Black Sesame Technologies được ra mắt vào tháng 4/ 2023. Đây là nền tảng SoC điện toán đa lĩnh vực đầu tiên trong ngành được thiết kế dành cho xe thông minh, đáp ứng các yêu cầu cao nhất về an toàn và độ tin cậy cấp ô tô. Trong đó, chip C1236 hướng đến khả năng lái xe thông minh tiên tiến, hỗ trợ tích hợp NOA (Tiếng ồn, Đến nơi và Chế độ lái tự động) trên một chip duy nhất; chip C1296 hỗ trợ hợp nhất đa lĩnh vực trên một chip duy nhất. Dựa trên dòng sản phẩm C1200, Black Sesame Technologies đã hợp tác với nhiều khách hàng, bao gồm các nhà sản xuất thiết bị gốc (OEM) và các đối tác trong hệ sinh thái như FAW Hongqi, Wind River, Junlian Intelligent và Banma Zhixing.

Vào tháng 3 năm nay, ChipEngine đã chính thức ra mắt chip lái xe tự hành cao cấp "Star One" 7nm dành cho mọi tình huống, cùng với các giải pháp buồng lái thông minh và lái xe thông minh tương ứng. Chip này dự kiến sẽ được triển khai rộng rãi trong các phương tiện vào năm tới. Chip này sử dụng quy trình sản xuất 7nm đạt chuẩn ô tô, tuân thủ tiêu chuẩn AEC-Q100 và tích hợp kiến trúc đa lõi không đồng nhất để tăng cường sức mạnh tính toán cho việc lái xe thông minh. Sức mạnh tính toán của CPU đạt 250 KDMIPS, và sức mạnh tính toán của NPU đạt 512 TOPS, đạt công suất tính toán tối đa 2048 TOPS thông qua sự hợp tác đa chip.

Bộ xử lý lượng tử vẫn đang trong giai đoạn xây dựng cơ sở.

Đầu năm nay, một số người tin rằng "bộ xử lý lượng tử sẽ bước vào giai đoạn khám phá ứng dụng thực tiễn vào năm 2025". Nhìn lại bây giờ, nhận định này về cơ bản là đúng, nhưng vẫn còn quá sớm để nói rằng chúng đã "có tính ứng dụng thực tiễn".

Gần đây, gã khổng lồ công nghệ IBM đã cho ra mắt hai chip lượng tử thử nghiệm – Loon và Nighthawk. Tuy nhiên, theo lộ trình được sửa đổi gần đây, IBM đã vạch ra một lộ trình từ năm 2025 đến năm 2033 và xa hơn nữa. Lộ trình cho thấy Kookaburra, được đề cập trong dự báo trước đó, sẽ được ra mắt vào năm 2026. Đây sẽ là mô-đun bộ xử lý lượng tử đầu tiên có khả năng lưu trữ thông tin trong bộ nhớ qLDPC và xử lý nó thông qua một LPU bổ sung, mở rộng các hệ thống chịu lỗi vượt ra ngoài một chip đơn lẻ.

Vào năm 2027, Cockatoo sẽ sử dụng bộ ghép L để tạo ra sự vướng víu lượng tử giữa hai mô-đun Kookaburra, từ đó kết nối các chip lượng tử với nhau như các nút trong một hệ thống lớn, tránh được việc phải chế tạo các chip lớn không thực tế. Vào năm 2029, họ sẽ cho ra mắt máy tính lượng tử chịu lỗi quy mô lớn đầu tiên trên thế giới - IBM Quantum Starling.

Những thành tựu này có ý nghĩa khoa học to lớn, chứng minh tính khả thi của điện toán lượng tử chịu lỗi, nhưng vẫn còn một thời gian dài nữa trước khi chúng sẵn sàng cho ứng dụng hoàn thiện. Bộ xử lý lượng tử vẫn là "công nghệ của tương lai", và những tiến bộ trong năm 2025 chủ yếu là "đặt nền móng" hơn là "xây dựng ngôi nhà".

Công nghệ quang tử silicon và CPO: Kỷ nguyên 1.6T lặng lẽ bắt đầu

Khi các cụm AI tiến gần đến giới hạn về băng thông và mức tiêu thụ điện năng, việc tích hợp quang tử silicon và quang học đóng gói chung (CPO) đã trở thành những lựa chọn phổ biến.

Vào năm 2025, Broadcom, Cisco và Ayar Labs đã cùng nhau quảng bá công nghệ CPO, giúp giảm đáng kể mức tiêu thụ điện năng trong quá trình chuyển đổi từ 800G lên 1.6T. Meta và Microsoft đã thử nghiệm các thiết bị chuyển mạch CPO trong một số cụm AI để xác minh độ tin cậy của chúng.

TSMC đã kết hợp thành công công nghệ quang học đóng gói đồng thời (CPO) với công nghệ đóng gói bán dẫn tiên tiến. Dự kiến các mẫu thử nghiệm sẽ bắt đầu vào đầu năm 2025, một thành tựu báo hiệu sự gia nhập của TSMC vào kỷ nguyên truyền dẫn quang 1.6T trong cùng năm đó. Các dự báo trong ngành cho thấy Broadcom và Nvidia có khả năng nằm trong số những người dùng đầu tiên của giải pháp TSMC.

LightCounting dự đoán rằng lượng xuất xưởng toàn cầu của các mô-đun quang 800G sẽ vượt quá 5 triệu đơn vị vào năm 2025, với các giải pháp LPO dự kiến chiếm hơn 40%, so với con số dưới 500.000 đơn vị vào năm 2023. Các mô-đun quang 800G, đặc biệt là những mô-đun sử dụng công nghệ LPO, đang trong giai đoạn phát triển nhanh chóng, đóng vai trò ngày càng quan trọng trong kỷ nguyên bùng nổ sức mạnh tính toán AI và liên tục thúc đẩy sự định hình lại và chuyển đổi của bối cảnh kết nối quang học trung tâm dữ liệu.

Tiếp nối mô-đun quang 800G, khi các cụm máy chủ AI đặt ra yêu cầu cao hơn về tốc độ kết nối, NVIDIA đã chọn chuyển sang sử dụng mô-đun quang 1.6T trong các máy chủ GB300 của mình, đồng thời cung cấp tùy chọn nâng cấp lên mô-đun quang 1.6T trong các máy chủ GB200. Như vậy, mô-đun quang 1.6T đang dần trở nên phổ biến.

Về dự báo phát triển trong tương lai, tốc độ sẽ đạt 1,6T trong vòng 1-2 năm tới. Dự kiến đến năm 2029, tốc độ mô-đun quang học cho các ứng dụng AI sẽ đạt 3,2T, và đến năm 2030, tốc độ 3,2T sẽ được sử dụng rộng rãi.

Bước vào chiến trường cốt lõi của điện toán AI

Đến năm 2025, RISC-V sẽ không còn chỉ là từ đồng nghĩa với "MCU tiết kiệm năng lượng" mà sẽ chính thức tham gia vào lĩnh vực điện toán trí tuệ nhân tạo.

Trên thực tế, ngay từ năm 2024, bộ xử lý RISC-V hiệu năng cao mã nguồn mở thế hệ thứ ba "Xiangshan" do Viện Công nghệ Máy tính thuộc Viện Hàn lâm Khoa học Trung Quốc và Viện Nghiên cứu Chip Mã nguồn Mở Bắc Kinh phát hành đã lọt vào nhóm hàng đầu về hiệu năng. Ngoài ra, một số công ty trong nước như Nuclei Technology, Easiway và Jinze Technology đã phát hành IP, bộ công cụ, nền tảng phần mềm, chip PC AI, MCU AI, bộ xử lý đa phương tiện và các chip khác, cũng như bo mạch phát triển và các sản phẩm khác.

Xét từ tiến trình hiện tại, RISC-V đang đồng thời tiến vào ba lĩnh vực có giá trị cao: trí tuệ nhân tạo biên (edge AI), xe thông minh và trung tâm dữ liệu. Nó không còn bị giới hạn ở các thiết bị IoT công suất thấp, mà thể hiện khả năng thâm nhập đa cấp: nó có thể được nhúng vào chip đánh thức bằng giọng nói, hỗ trợ hệ thống ra quyết định của xe thông minh, và thậm chí trở thành nền tảng đáng tin cậy của trung tâm dữ liệu đám mây.

Trong quá trình thúc đẩy sự tích hợp sâu rộng giữa RISC-V và AI, các công ty như ESW Computing, China Mobile ChipStar và Advanced Spacetime đều đã có những đóng góp đáng kể. Trong lĩnh vực ô tô, Infineon và Mobileye đã liên tiếp cho ra mắt các giải pháp ADAS. NVIDIA đang tích cực thúc đẩy việc chuyển đổi CUDA sang kiến trúc RISC-V, điều này có nghĩa là các nhà phát triển có thể tự do lựa chọn kiến trúc CPU cho trung tâm dữ liệu, và sẽ thúc đẩy ứng dụng rộng rãi của RISC-V trong lĩnh vực điện toán hiệu năng cao ở cấp độ hệ sinh thái.

RISC-V International dự đoán rằng đến năm 2031, chip RISC-V sẽ chiếm thị phần đáng kể trong sáu thị trường chính: điện tử tiêu dùng (39%), máy tính (33%), ô tô (31%), trung tâm dữ liệu (28%), công nghiệp (27%) và truyền thông mạng (26%), với tổng số lượng xuất xưởng vượt quá 20 tỷ đơn vị.

Màn hình SiC 8 inch bắt đầu sản xuất hàng loạt

Vào năm 2025, ngành công nghiệp silicon carbide sẽ chính thức bước vào giai đoạn chuyển đổi sang sản xuất tấm wafer 8 inch, với các công ty như STMicroelectronics, Coretronic, Rohm, Resonac và ON Semiconductor đều đã đi vào hoạt động các nhà máy sản xuất wafer SiC 8 inch.

Nâng cấp từ tấm wafer silicon carbide 6 inch lên 8 inch làm tăng chi phí xử lý chất nền, nhưng lại giúp tăng năng suất chip. Một tấm wafer 8 inch có thể sản xuất số lượng chip nhiều gấp khoảng 1,8 lần so với tấm wafer silicon carbide 6 inch. Việc chuyển sang sử dụng wafer 8 inch là một cách khả thi để giảm chi phí sản xuất thiết bị silicon carbide. Hơn nữa, độ dày chất nền tăng lên ở wafer 8 inch giúp duy trì hình dạng trong quá trình xử lý, giảm hiện tượng cong vênh cạnh và giảm mật độ khuyết tật, từ đó cải thiện năng suất. Sử dụng chất nền 8 inch có thể giảm đáng kể chi phí đơn vị tổng thể.

Trong số các công ty Trung Quốc, Tianyue Advanced, Tianke Heda và Sanan Optoelectronics đều đã đạt được khả năng sản xuất hàng loạt quy mô lớn. Năng lực sản xuất chất nền của Tianyue Advanced, chủ yếu là tấm wafer 8 inch, đạt 460.000 tấm wafer/năm vào năm 2024, và mục tiêu tổng năng lực sản xuất là tăng lên 600.000 tấm wafer/năm vào năm 2025. Nhà máy Lingang, Thượng Hải của công ty đã đạt năng lực sản xuất hàng năm là 300.000 chất nền dẫn điện vào giữa năm 2024 và hiện đang thúc đẩy giai đoạn mở rộng năng lực sản xuất thứ hai. Các cơ sở Jinan và Jining đã hình thành chuỗi cung ứng hợp tác với cơ sở Lingang.

Năm 2024, Tianke Heda đã đạt được sản xuất hàng loạt chất nền 8 inch. Đến năm 2025, tổng công suất sản xuất chất nền dự kiến đạt từ 500.000 đến 800.000 tấm wafer (bao gồm cả wafer 8 inch), và công suất sản xuất wafer epitaxy là 250.000 tấm. Với các cơ sở tại Bắc Kinh và Từ Châu làm nòng cốt, liên doanh Thâm Quyến đã tái đầu tư vào Tianke để tiếp tục tăng cường năng lực sản xuất chất nền 6-8 inch và wafer epitaxy. Hơn nữa, các sản phẩm 8 inch đã được các nhà sản xuất thiết bị lớn trong và ngoài nước kiểm chứng và đã nhận được các đơn đặt hàng sản xuất hàng loạt LTA trong nhiều năm.

Trong nửa đầu năm 2025, cơ sở tại Hồ Nam của Sanan Optoelectronics có công suất sản xuất đế 8 inch là 1.000 tấm wafer/tháng và công suất sản xuất lớp màng mỏng (epitaxial) là 2.000 tấm wafer/tháng. Cơ sở tại Trùng Khánh, một liên doanh với STMicroelectronics, dự kiến có công suất sản xuất đế 8 inch là 480.000 tấm wafer/năm. Cơ sở này đã được đưa vào hoạt động và cung cấp mẫu để kiểm chứng vào tháng 2 năm 2025.

Tấm silicon carbide 8 inch đang thúc đẩy sự bùng nổ của nhiều kịch bản ứng dụng. Trong lĩnh vực xe điện, nền tảng 800V đã trở thành tiêu chuẩn. Trong lĩnh vực quang điện, các thiết bị silicon carbide có hiệu suất trên 98%, và các giải pháp tích hợp quang điện và lưu trữ năng lượng đã trở thành tiêu chuẩn ngành. Ngoài ra, tại các thị trường mới nổi, chất nền 8 inch có thể sản xuất 3-4 cặp kính AR, và việc giảm chi phí sẽ đẩy nhanh sự phát triển của kính AR và các ứng dụng khác.

Trí tuệ nhân tạo + Phân tích dữ liệu khám phá (EDA): Tầm quan trọng của nó ngày càng nổi bật

Đến năm 2025, trí tuệ nhân tạo (AI) sẽ không chỉ còn là "công cụ tăng tốc" trong quy trình thiết kế mạch điện tử (EDA), mà sẽ bắt đầu định hình lại mô hình thiết kế chip.

Phần mềm DSO.ai của Synopsys được sử dụng rộng rãi trong thiết kế các nút công nghệ dưới 2nm. Nó có thể tự động tìm kiếm phương án bố trí và định tuyến tối ưu mà không cần can thiệp thủ công, đạt được sự cải thiện tổng thể về PPA (hiệu năng, điện năng tiêu thụ, diện tích) hơn 10%.

Công nghệ NVIDIA cuLitho sử dụng các cụm GPU để tăng tốc các phép tính OPC (Hiệu chỉnh khoảng cách quang học), rút ngắn quá trình tạo mặt nạ từ nhiều tuần xuống còn vài giờ, nhanh hơn tới 40 lần.

SemiKong, mô hình lớn mã nguồn mở của Aitomatic, hỗ trợ các quy tắc thiết kế truy vấn ngôn ngữ tự nhiên, tự động tạo các đoạn mã Verilog và hỗ trợ định vị lỗi. Nó đã được một số công ty khởi nghiệp sử dụng để tạo mẫu nhanh.

AI+EDA đang làm giảm rào cản gia nhập thị trường thiết kế chip cao cấp.

Nhìn lại mười dự đoán hàng đầu được đưa ra vào đầu năm, hầu hết các hướng đi đều tiến triển theo kế hoạch, một số bị chậm lại một chút, và một số thậm chí còn vượt quá mong đợi. Đứng trước ngưỡng cửa năm 2025 và hướng tới năm 2026, bước đột phá công nghệ tiếp theo có thể không còn xa nữa, nó nằm trong những nhà máy sản xuất chip đang âm thầm mở rộng sản xuất, trong nhật ký về việc tăng năng suất và trong từng dòng mã được các kỹ sư gõ ra.