Mai Nhung

Writer

Một quyết định chiến lược quan trọng vừa được TSMC hé lộ tại hội thảo công nghệ NA Technology Symposium gần đây, có khả năng định hình lại cuộc đua công nghệ bán dẫn trong vài năm tới. Gã khổng lồ đúc chip Đài Loan xác nhận họ sẽ không sử dụng công nghệ quang khắc cực tím siêu cực đại khẩu độ cao (High-NA EUV) thế hệ mới nhất cho tiến trình A14 (tương đương 1.4nm) dự kiến bắt đầu sản xuất vào năm 2028. Thay vào đó, TSMC sẽ tiếp tục dựa vào công nghệ EUV khẩu độ 0.33 (0.33-NA) hiện tại, kết hợp với các kỹ thuật đa mẫu (multi-patterning) phức tạp hơn.

Chi phí là rào cản chính

Lý do cốt lõi đằng sau quyết định có phần bất ngờ này, theo Phó chủ tịch cấp cao Kevin Zhang của TSMC, chính là chi phí. Các hệ thống máy quang khắc High-NA EUV (thế hệ tiếp theo của EUV) cực kỳ đắt đỏ, ước tính có thể làm tăng tổng chi phí sản xuất chip lên gấp 2,5 lần so với việc sử dụng máy EUV 0.33-NA hiện tại. Đây là một khoản chi phí khổng lồ khó có thể chấp nhận đối với các sản phẩm thương mại cần đảm bảo tính cạnh tranh về giá.

Ông Zhang cho biết, từ tiến trình 2nm (N2, bắt đầu sản xuất cuối năm nay) cho đến A14, TSMC tin rằng họ vẫn có thể đạt được mật độ và độ phức tạp cần thiết bằng cách tối ưu hóa việc sử dụng 0.33-NA EUV và kỹ thuật đa mẫu, đồng thời cố gắng giảm thiểu số lượng mặt nạ (mask) phải sử dụng thêm – một yếu tố quan trọng để kiểm soát chi phí sản xuất hiệu quả.

Intel đi trước về High-NA EUV?

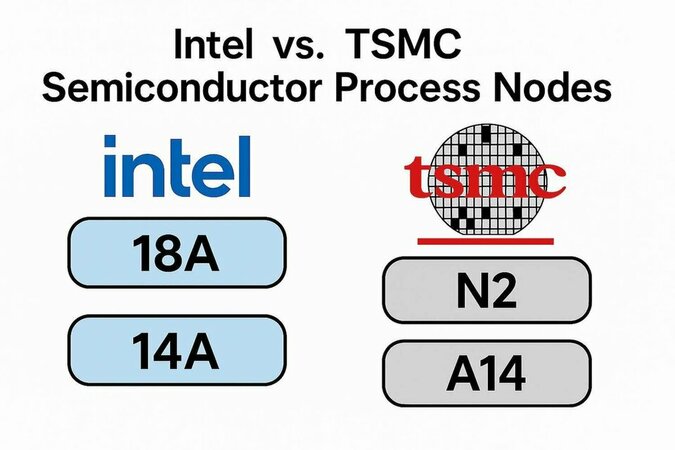

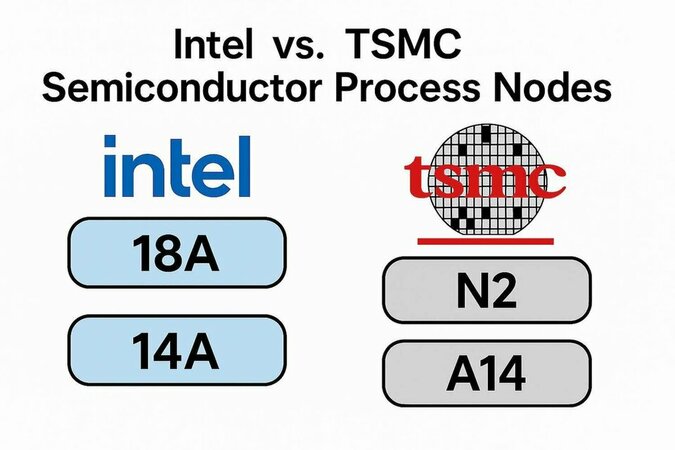

Quyết định này của TSMC tạo ra một sự tương phản rõ rệt với đối thủ trực tiếp là Intel. Intel Foundry Services (IFS) đang đặt cược lớn vào High-NA EUV và dự kiến sẽ là công ty đầu tiên trên thế giới triển khai công nghệ này ở quy mô thương mại với tiến trình 18A (tương đương 1.8nm), mục tiêu vào cuối năm 2025 hoặc đầu năm 2026. Điều này đồng nghĩa với việc Intel có thể sẽ đi trước TSMC ít nhất 3-4 năm trong việc làm chủ và áp dụng công nghệ quang khắc tiên tiến nhất vào sản xuất hàng loạt.

Tuy nhiên, TSMC không hoàn toàn từ bỏ High-NA EUV. Hãng cho biết dự kiến sẽ áp dụng công nghệ này cho tiến trình A14P – một phiên bản nâng cấp của A14, có thể ra mắt sau năm 2029.

Một canh bạc chiến lược?

Việc TSMC trì hoãn áp dụng High-NA EUV cho tiến trình A14 có thể được xem là một "canh bạc" chiến lược. Ưu điểm là giúp công ty tiết kiệm chi phí đầu tư khổng lồ trong ngắn hạn, tối ưu hóa hiệu quả của các dây chuyền 0.33-NA EUV hiện có mà họ đã làm chủ rất tốt. Tuy nhiên, nhược điểm là nó có thể khiến TSMC tạm thời mất đi vị thế dẫn đầu về công nghệ quang khắc trong mắt khách hàng và giới đầu tư vào giai đoạn 2026-2029, khi Intel đã triển khai High-NA. Thành công của chiến lược này sẽ phụ thuộc rất nhiều vào việc liệu tiến trình A14 (sử dụng 0.33-NA EUV + multi-patterning) có thực sự cạnh tranh được về hiệu năng và chi phí so với tiến trình 18A (sử dụng High-NA EUV) của Intel hay không, cũng như độ trưởng thành và hiệu quả chi phí của High-NA EUV khi TSMC chính thức áp dụng nó cho A14P.

#Cuộcchiếnbándẫn

Chi phí là rào cản chính

Lý do cốt lõi đằng sau quyết định có phần bất ngờ này, theo Phó chủ tịch cấp cao Kevin Zhang của TSMC, chính là chi phí. Các hệ thống máy quang khắc High-NA EUV (thế hệ tiếp theo của EUV) cực kỳ đắt đỏ, ước tính có thể làm tăng tổng chi phí sản xuất chip lên gấp 2,5 lần so với việc sử dụng máy EUV 0.33-NA hiện tại. Đây là một khoản chi phí khổng lồ khó có thể chấp nhận đối với các sản phẩm thương mại cần đảm bảo tính cạnh tranh về giá.

Ông Zhang cho biết, từ tiến trình 2nm (N2, bắt đầu sản xuất cuối năm nay) cho đến A14, TSMC tin rằng họ vẫn có thể đạt được mật độ và độ phức tạp cần thiết bằng cách tối ưu hóa việc sử dụng 0.33-NA EUV và kỹ thuật đa mẫu, đồng thời cố gắng giảm thiểu số lượng mặt nạ (mask) phải sử dụng thêm – một yếu tố quan trọng để kiểm soát chi phí sản xuất hiệu quả.

Intel đi trước về High-NA EUV?

Quyết định này của TSMC tạo ra một sự tương phản rõ rệt với đối thủ trực tiếp là Intel. Intel Foundry Services (IFS) đang đặt cược lớn vào High-NA EUV và dự kiến sẽ là công ty đầu tiên trên thế giới triển khai công nghệ này ở quy mô thương mại với tiến trình 18A (tương đương 1.8nm), mục tiêu vào cuối năm 2025 hoặc đầu năm 2026. Điều này đồng nghĩa với việc Intel có thể sẽ đi trước TSMC ít nhất 3-4 năm trong việc làm chủ và áp dụng công nghệ quang khắc tiên tiến nhất vào sản xuất hàng loạt.

Tuy nhiên, TSMC không hoàn toàn từ bỏ High-NA EUV. Hãng cho biết dự kiến sẽ áp dụng công nghệ này cho tiến trình A14P – một phiên bản nâng cấp của A14, có thể ra mắt sau năm 2029.

Một canh bạc chiến lược?

Việc TSMC trì hoãn áp dụng High-NA EUV cho tiến trình A14 có thể được xem là một "canh bạc" chiến lược. Ưu điểm là giúp công ty tiết kiệm chi phí đầu tư khổng lồ trong ngắn hạn, tối ưu hóa hiệu quả của các dây chuyền 0.33-NA EUV hiện có mà họ đã làm chủ rất tốt. Tuy nhiên, nhược điểm là nó có thể khiến TSMC tạm thời mất đi vị thế dẫn đầu về công nghệ quang khắc trong mắt khách hàng và giới đầu tư vào giai đoạn 2026-2029, khi Intel đã triển khai High-NA. Thành công của chiến lược này sẽ phụ thuộc rất nhiều vào việc liệu tiến trình A14 (sử dụng 0.33-NA EUV + multi-patterning) có thực sự cạnh tranh được về hiệu năng và chi phí so với tiến trình 18A (sử dụng High-NA EUV) của Intel hay không, cũng như độ trưởng thành và hiệu quả chi phí của High-NA EUV khi TSMC chính thức áp dụng nó cho A14P.

#Cuộcchiếnbándẫn