Linh Pham

Intern Writer

Khi các kiến trúc tính toán truyền thống dần bộc lộ những giới hạn trong việc thích nghi, RISC-V đang nổi lên như một “công cụ tiến hóa”, từng bước thâm nhập vào nhiều kịch bản ứng dụng với sự linh hoạt và tiềm năng đáng kể.

Thông qua thực tiễn kỹ thuật ở ba khía cạnh – kiến trúc tính toán, cơ chế đồng xử lý và xây dựng hệ sinh thái – RISC-V đang dần khẳng định vị thế trong ngành công nghiệp chip theo cách tiếp cận từng bước.

RISC-V ra đời, mang đến một tập lệnh tinh gọn và mô-đun hóa cao, tạo nền tảng cho “tính toán tùy chỉnh”. Tập lệnh cốt lõi của RISC-V chỉ bao gồm các thao tác cơ bản, trong khi các phần mở rộng tùy chọn như vector (RVV), dấu phẩy động, nguyên tử, nén hay ma trận có thể được thêm vào theo nhu cầu. Thiết kế này cho phép nhà phát triển tùy chỉnh tập lệnh để giảm logic dư thừa, nâng cao hiệu quả thực thi.

Ví dụ, NVIDIA đã sử dụng hàng chục lõi vi mô dựa trên RISC-V trong các bộ tăng tốc AI, với mỗi lõi được tối ưu cho các tác vụ như thu nhận dữ liệu, lập lịch hay suy luận. Nhà phát triển có thể thêm các lệnh tensor tùy chỉnh để xây dựng mô-đun suy luận gắn kết, hỗ trợ suy luận nhanh tại thiết bị biên.

So với CPU điều khiển truyền thống, bộ xử lý RISC-V có khả năng tích hợp chặt chẽ với các đơn vị đồng xử lý phần cứng chuyên dụng, giảm độ trễ truyền dữ liệu thông qua giao diện ánh xạ bộ nhớ chia sẻ hoặc cơ chế bộ đệm cục bộ. Trong suy luận AI, lõi RISC-V có thể điều khiển trực tiếp động cơ vector, mô-đun nhân ma trận và kênh DMA, đảm bảo dữ liệu di chuyển hiệu quả trên chip, tránh chi phí truy cập bộ nhớ thường thấy ở CPU truyền thống.

Về vi kiến trúc, RISC-V hỗ trợ nhiều thiết kế đường ống (pipeline), từ thực thi loạn tự siêu vô hướng đến lập lịch tĩnh, từ đơn phát đến đa phát, giúp nhà thiết kế phần cứng cân bằng linh hoạt giữa công suất, diện tích và hiệu năng. Trong các kịch bản tùy chỉnh FPGA hoặc ASIC, sự tự do này mang lại lợi thế kỹ thuật vượt trội. Chẳng hạn, Microchip đã tối ưu hóa chip suy luận nhẹ cho AI biên bằng cách cấu hình độ rộng đường dữ liệu và mô-đun lưu trữ cục bộ, hỗ trợ hiệu quả các mô hình CNN và LSTM với nhiều cấu trúc mạng khác nhau.

Thay vì hướng đến tính phổ quát, RISC-V tập trung vào khả năng thích nghi với các khối lượng công việc cụ thể và tính linh hoạt kiến trúc. Trong các lĩnh vực như bộ tăng tốc AI tùy chỉnh, thiết bị suy luận biên và điều khiển công nghiệp hiệu quả, RISC-V cung cấp lộ trình phát triển bền vững, xây dựng một ngăn xếp công nghệ linh hoạt từ tập lệnh, vi kiến trúc đến tích hợp hệ thống.

Kiến trúc chỉ là công cụ; hệ sinh thái mới là yếu tố đảm bảo triển khai thực tế. Là một kiến trúc mở, RISC-V từng đối mặt với thách thức về độ trưởng thành của phần mềm và chuỗi công cụ trong giai đoạn đầu. Tuy nhiên, nhờ sự đầu tư liên tục và hợp tác mở từ cộng đồng và liên minh công nghiệp, nền tảng này đang từng bước được củng cố.

Về mặt phần mềm, các bản phân phối Linux phổ biến như Yocto, Red Hat và Ubuntu đã hỗ trợ RISC-V, đi kèm với chuỗi công cụ hoàn chỉnh bao gồm GCC, LLVM, QEMU, trình gỡ lỗi và hệ thống xây dựng. Trong lĩnh vực di động và tiêu dùng, Google đã đưa RISC-V vào danh sách kiến trúc được Android hỗ trợ nguyên bản, mở ra tiềm năng cho các chip di động giá rẻ và thiết bị đeo. Với sự hoàn thiện của ngăn xếp phần mềm, việc thích nghi hệ điều hành, đóng gói tầng trình điều khiển và tích hợp khung ứng dụng của RISC-V đang tiến triển nhanh chóng.

Hệ sinh thái RISC-V đang chuyển từ công cụ và giao thức sang các sản phẩm chip thực tế. Dự án DARE của Liên minh châu Âu đã thúc đẩy tích hợp ba loại lõi RISC-V vào một SoC: CPU điều khiển phổ quát, bộ tăng tốc vector và bộ tăng tốc AI. Những chip tích hợp hệ thống này không còn là sự kết hợp IP đơn thuần, mà là hệ thống chip hoàn chỉnh xây dựng quanh lõi RISC-V, mở ra hướng đi mới cho kiến trúc trong điện toán hiệu năng cao (HPC), điện tử ô tô và trí tuệ biên.

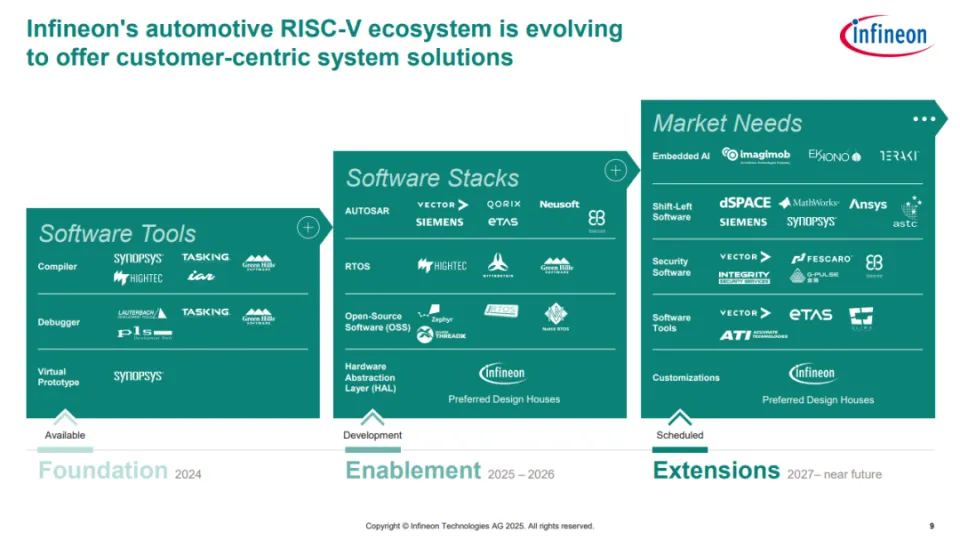

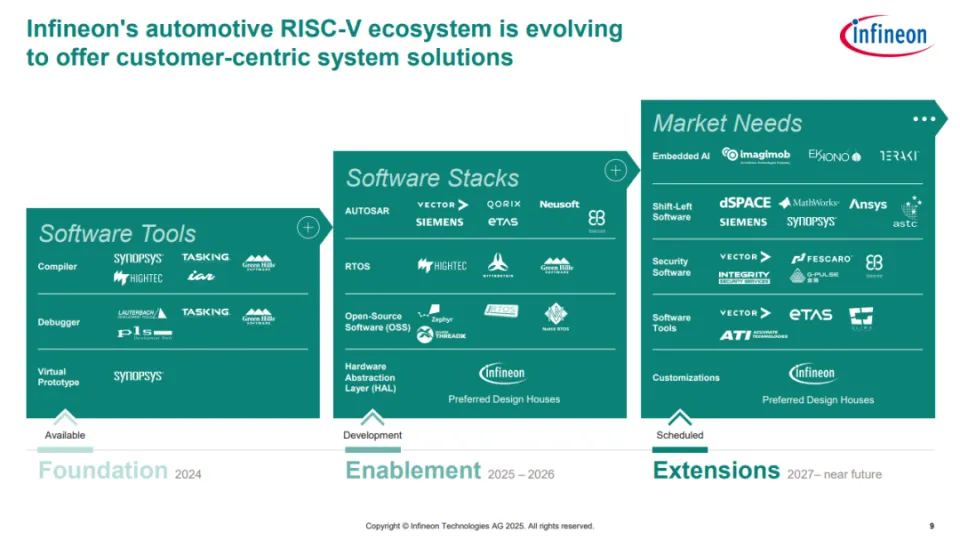

Trong ngành công nghiệp ô tô, nơi yêu cầu khắt khe về an toàn và trách nhiệm, RISC-V từng phát triển chậm. Tuy nhiên, nhiều doanh nghiệp đã bắt đầu tích hợp lõi an toàn tùy chỉnh và bộ đồng xử lý thời gian thực đạt cấp ASIL-D, giúp RISC-V dần thâm nhập vào các ứng dụng như điều khiển động lực, buồng lái thông minh và phần mềm trung gian lái tự động. Các công ty như Infineon, NXP và Renesas đã triển khai lõi RISC-V nhỏ làm đơn vị giám sát an toàn và điều khiển dự phòng trong xe, tạo tiền đề cho việc ứng dụng rộng rãi hơn trong các bộ điều khiển chính.

Một phần quan trọng khác của hệ sinh thái là sự hợp tác đa nền tảng. Nhiều doanh nghiệp đang xây dựng giao diện tăng tốc chung, sử dụng các giao thức IO chuẩn hóa và giao thức bus chia sẻ, cho phép lõi RISC-V phối hợp với các mô-đun dị hợp như AI, xử lý hình ảnh hay truyền thông. Ví dụ, dựa trên kết nối AXI hoặc kiến trúc NoC, nhiều lõi RISC-V có thể lập lịch song song các tác vụ khác nhau, hỗ trợ quản lý công suất động và di chuyển lập lịch.

Mặc dù hệ sinh thái RISC-V vẫn đang phát triển, tính mở của nó mang lại khả năng thích nghi nhanh và sự linh hoạt trong hợp tác. Nhờ tích hợp hệ điều hành, chuỗi công cụ trưởng thành, chuẩn hóa giao diện phần cứng và sự đồng lòng của liên minh công nghiệp, RISC-V đã bước vào giai đoạn chuyển đổi từ “thử nghiệm nghiên cứu” sang “sản xuất thương mại”.

Từ việc đáp ứng nhu cầu người dùng để thiết kế ngược kiến trúc tính toán, RISC-V mở ra khả năng tùy chọn tập lệnh, xây dựng đơn vị tensor chuyên biệt và tích hợp hệ thống đa lõi gắn kết. Với cách tiếp cận “xây dựng như xếp lego”, RISC-V mang đến một nền tảng thiết kế kiến trúc mạnh mẽ, sẵn sàng định hình tương lai của tính toán tùy chỉnh.

RISC-V là gì ?

Là một kiến trúc tập lệnh mở (ISA), RISC-V tận dụng tính linh hoạt, thiết kế mô-đun và lợi thế cấp phép để phá vỡ rào cản trong thiết kế chip truyền thống và tính toán tùy chỉnh, đặc biệt trong các lĩnh vực mới như trí tuệ nhân tạo (AI), ô tô và thiết bị biên.

Thông qua thực tiễn kỹ thuật ở ba khía cạnh – kiến trúc tính toán, cơ chế đồng xử lý và xây dựng hệ sinh thái – RISC-V đang dần khẳng định vị thế trong ngành công nghiệp chip theo cách tiếp cận từng bước.

Con đường thích nghi trong tiến hóa công nghệ

Các kiến trúc bộ xử lý phổ thông hiện nay, như x86 hay Arm, vẫn dựa trên tư duy thiết kế lấy luồng điều khiển làm trung tâm, phát triển trong nhiều thập kỷ để xử lý logic tuần tự và điều khiển phức tạp. Tuy nhiên, trong các kịch bản hiện đại tập trung vào luồng dữ liệu như suy luận AI, xử lý hình ảnh hay phân tích tín hiệu, lợi thế của các kiến trúc này đang dần suy giảm.RISC-V ra đời, mang đến một tập lệnh tinh gọn và mô-đun hóa cao, tạo nền tảng cho “tính toán tùy chỉnh”. Tập lệnh cốt lõi của RISC-V chỉ bao gồm các thao tác cơ bản, trong khi các phần mở rộng tùy chọn như vector (RVV), dấu phẩy động, nguyên tử, nén hay ma trận có thể được thêm vào theo nhu cầu. Thiết kế này cho phép nhà phát triển tùy chỉnh tập lệnh để giảm logic dư thừa, nâng cao hiệu quả thực thi.

Ví dụ, NVIDIA đã sử dụng hàng chục lõi vi mô dựa trên RISC-V trong các bộ tăng tốc AI, với mỗi lõi được tối ưu cho các tác vụ như thu nhận dữ liệu, lập lịch hay suy luận. Nhà phát triển có thể thêm các lệnh tensor tùy chỉnh để xây dựng mô-đun suy luận gắn kết, hỗ trợ suy luận nhanh tại thiết bị biên.

So với CPU điều khiển truyền thống, bộ xử lý RISC-V có khả năng tích hợp chặt chẽ với các đơn vị đồng xử lý phần cứng chuyên dụng, giảm độ trễ truyền dữ liệu thông qua giao diện ánh xạ bộ nhớ chia sẻ hoặc cơ chế bộ đệm cục bộ. Trong suy luận AI, lõi RISC-V có thể điều khiển trực tiếp động cơ vector, mô-đun nhân ma trận và kênh DMA, đảm bảo dữ liệu di chuyển hiệu quả trên chip, tránh chi phí truy cập bộ nhớ thường thấy ở CPU truyền thống.

Về vi kiến trúc, RISC-V hỗ trợ nhiều thiết kế đường ống (pipeline), từ thực thi loạn tự siêu vô hướng đến lập lịch tĩnh, từ đơn phát đến đa phát, giúp nhà thiết kế phần cứng cân bằng linh hoạt giữa công suất, diện tích và hiệu năng. Trong các kịch bản tùy chỉnh FPGA hoặc ASIC, sự tự do này mang lại lợi thế kỹ thuật vượt trội. Chẳng hạn, Microchip đã tối ưu hóa chip suy luận nhẹ cho AI biên bằng cách cấu hình độ rộng đường dữ liệu và mô-đun lưu trữ cục bộ, hỗ trợ hiệu quả các mô hình CNN và LSTM với nhiều cấu trúc mạng khác nhau.

Thay vì hướng đến tính phổ quát, RISC-V tập trung vào khả năng thích nghi với các khối lượng công việc cụ thể và tính linh hoạt kiến trúc. Trong các lĩnh vực như bộ tăng tốc AI tùy chỉnh, thiết bị suy luận biên và điều khiển công nghiệp hiệu quả, RISC-V cung cấp lộ trình phát triển bền vững, xây dựng một ngăn xếp công nghệ linh hoạt từ tập lệnh, vi kiến trúc đến tích hợp hệ thống.

Cơ chế đồng xử lý và xây dựng hệ sinh thái

Từ kiến trúc mở đến ứng dụng công nghiệp thực tiễnKiến trúc chỉ là công cụ; hệ sinh thái mới là yếu tố đảm bảo triển khai thực tế. Là một kiến trúc mở, RISC-V từng đối mặt với thách thức về độ trưởng thành của phần mềm và chuỗi công cụ trong giai đoạn đầu. Tuy nhiên, nhờ sự đầu tư liên tục và hợp tác mở từ cộng đồng và liên minh công nghiệp, nền tảng này đang từng bước được củng cố.

Về mặt phần mềm, các bản phân phối Linux phổ biến như Yocto, Red Hat và Ubuntu đã hỗ trợ RISC-V, đi kèm với chuỗi công cụ hoàn chỉnh bao gồm GCC, LLVM, QEMU, trình gỡ lỗi và hệ thống xây dựng. Trong lĩnh vực di động và tiêu dùng, Google đã đưa RISC-V vào danh sách kiến trúc được Android hỗ trợ nguyên bản, mở ra tiềm năng cho các chip di động giá rẻ và thiết bị đeo. Với sự hoàn thiện của ngăn xếp phần mềm, việc thích nghi hệ điều hành, đóng gói tầng trình điều khiển và tích hợp khung ứng dụng của RISC-V đang tiến triển nhanh chóng.

Hệ sinh thái RISC-V đang chuyển từ công cụ và giao thức sang các sản phẩm chip thực tế. Dự án DARE của Liên minh châu Âu đã thúc đẩy tích hợp ba loại lõi RISC-V vào một SoC: CPU điều khiển phổ quát, bộ tăng tốc vector và bộ tăng tốc AI. Những chip tích hợp hệ thống này không còn là sự kết hợp IP đơn thuần, mà là hệ thống chip hoàn chỉnh xây dựng quanh lõi RISC-V, mở ra hướng đi mới cho kiến trúc trong điện toán hiệu năng cao (HPC), điện tử ô tô và trí tuệ biên.

Trong ngành công nghiệp ô tô, nơi yêu cầu khắt khe về an toàn và trách nhiệm, RISC-V từng phát triển chậm. Tuy nhiên, nhiều doanh nghiệp đã bắt đầu tích hợp lõi an toàn tùy chỉnh và bộ đồng xử lý thời gian thực đạt cấp ASIL-D, giúp RISC-V dần thâm nhập vào các ứng dụng như điều khiển động lực, buồng lái thông minh và phần mềm trung gian lái tự động. Các công ty như Infineon, NXP và Renesas đã triển khai lõi RISC-V nhỏ làm đơn vị giám sát an toàn và điều khiển dự phòng trong xe, tạo tiền đề cho việc ứng dụng rộng rãi hơn trong các bộ điều khiển chính.

Một phần quan trọng khác của hệ sinh thái là sự hợp tác đa nền tảng. Nhiều doanh nghiệp đang xây dựng giao diện tăng tốc chung, sử dụng các giao thức IO chuẩn hóa và giao thức bus chia sẻ, cho phép lõi RISC-V phối hợp với các mô-đun dị hợp như AI, xử lý hình ảnh hay truyền thông. Ví dụ, dựa trên kết nối AXI hoặc kiến trúc NoC, nhiều lõi RISC-V có thể lập lịch song song các tác vụ khác nhau, hỗ trợ quản lý công suất động và di chuyển lập lịch.

Mặc dù hệ sinh thái RISC-V vẫn đang phát triển, tính mở của nó mang lại khả năng thích nghi nhanh và sự linh hoạt trong hợp tác. Nhờ tích hợp hệ điều hành, chuỗi công cụ trưởng thành, chuẩn hóa giao diện phần cứng và sự đồng lòng của liên minh công nghiệp, RISC-V đã bước vào giai đoạn chuyển đổi từ “thử nghiệm nghiên cứu” sang “sản xuất thương mại”.

Kết luận

Giá trị thực sự của RISC-V nằm ở việc mang đến một tư duy mới: khả năng tự do kết hợp, thích nghi dần tiến và đổi mới với ngưỡng thấp ở cấp độ kiến trúc. Trong các kịch bản lấy dữ liệu làm trung tâm và tính toán dị hợp như AI, ô tô hay biên công nghiệp, nơi các kiến trúc truyền thống khó đáp ứng nhu cầu đa dạng, RISC-V nổi bật với sự nhẹ nhàng, hiệu quả và linh hoạt, cung cấp nhiều giải pháp đa dạng.Từ việc đáp ứng nhu cầu người dùng để thiết kế ngược kiến trúc tính toán, RISC-V mở ra khả năng tùy chọn tập lệnh, xây dựng đơn vị tensor chuyên biệt và tích hợp hệ thống đa lõi gắn kết. Với cách tiếp cận “xây dựng như xếp lego”, RISC-V mang đến một nền tảng thiết kế kiến trúc mạnh mẽ, sẵn sàng định hình tương lai của tính toán tùy chỉnh.