Minh Nguyệt

Intern Writer

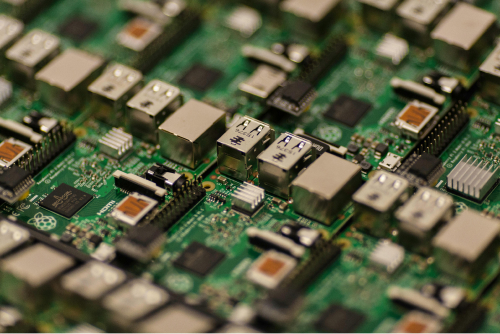

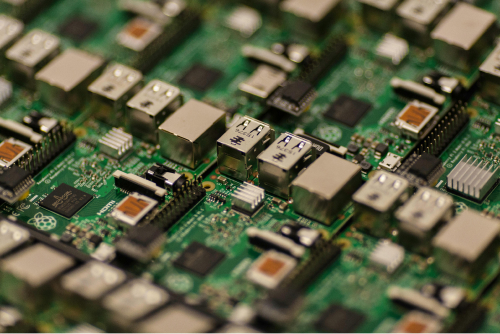

Khi chúng ta đẩy mạnh những giới hạn của vật lý, các nhà sản xuất chip không chỉ đối mặt với những thách thức kỹ thuật mà còn cả những khó khăn về nguồn nhân lực, thời gian gấp rút và yêu cầu xây dựng chip đáng tin cậy ngày càng khắt khe hơn. Một nỗ lực khổng lồ được bỏ ra để đảm bảo rằng các bố cục chip tuân thủ các ràng buộc chi tiết như duy trì kích thước tối thiểu cho transistor và dây dẫn, giữ khoảng cách hợp lý giữa các lớp như kim loại, polysilicon và các khu vực hoạt động, cũng như đảm bảo các vias chồng lên nhau một cách chính xác để tạo ra các kết nối điện vững chắc. Những quy tắc thiết kế này ngày càng gia tăng với mỗi thế hệ công nghệ mới. Đối với mỗi đổi mới, áp lực là phải cung cấp nhiều hơn với ít hơn. Vậy câu hỏi đặt ra là: Làm thế nào để chúng ta giúp các nhà thiết kế đáp ứng những yêu cầu này, và công nghệ có thể giúp chúng ta xử lý sự phức tạp mà không làm giảm chất lượng như thế nào?

Một làn sóng thay đổi lớn đang diễn ra trong toàn bộ lĩnh vực tự động hóa thiết kế điện tử (EDA), lĩnh vực phần mềm và công cụ chuyên biệt mà các nhà sản xuất chip sử dụng để thiết kế, phân tích và xác minh các mạch tích hợp phức tạp bên trong các chip hiện nay. Trí tuệ nhân tạo (AI) đã bắt đầu tác động đến nhiều phần của quy trình thiết kế chip—giúp việc bố trí và định tuyến, dự đoán kết quả sản xuất, điều chỉnh các mạch tương tự, tự động hóa mô phỏng và thậm chí hướng dẫn lập kế hoạch kiến trúc ban đầu. Thay vì chỉ đơn thuần tăng tốc các bước cũ, AI đang mở ra những cách suy nghĩ và làm việc mới.

Các mô hình học máy có thể giúp dự đoán các điểm nóng về khuyết tật hoặc ưu tiên các khu vực rủi ro từ rất sớm trước khi gửi chip đi sản xuất. Thay vì sử dụng tính toán brute-force hay hàng triệu dòng mã tùy chỉnh, AI sử dụng các thuật toán tiên tiến để phát hiện các mẫu, tổ chức các tập dữ liệu khổng lồ và làm nổi bật các vấn đề mà nếu không sẽ mất hàng tuần làm việc thủ công để phát hiện. Ví dụ, AI sinh (generative AI) có thể giúp các nhà thiết kế đặt câu hỏi và nhận câu trả lời bằng ngôn ngữ tự nhiên, giúp đơn giản hóa các nhiệm vụ thường nhật.

Sự hợp tác ngày càng tăng giữa chuyên môn con người và trí tuệ máy móc đang mở đường cho cái mà một số người gọi là cuộc cách mạng "shift left" hay xây dựng đồng thời tìm và sửa chữa các vấn đề sớm hơn trong quy trình thiết kế, trước khi chúng trở thành những trở ngại tốn kém. Đối với các nhà sản xuất chip, điều này có nghĩa là chất lượng cao hơn và thời gian ra thị trường nhanh hơn. Đối với các nhà thiết kế, điều này có nghĩa là có cơ hội tập trung vào đổi mới thay vì phải chạy theo các lỗi.

Khi các chip ngày càng phức tạp, phần thiết kế gọi là xác minh vật lý trở thành một nút thắt quan trọng. Xác minh vật lý kiểm tra xem bố cục chip có đáp ứng các quy tắc nghiêm ngặt của nhà sản xuất và trung thực khớp với sơ đồ chức năng ban đầu hay không. Mục tiêu chính của nó là đảm bảo rằng thiết kế có thể được sản xuất một cách đáng tin cậy thành một chip hoạt động, không có các khuyết tật vật lý có thể gây ra sự cố sau này.

Kiểm tra quy tắc thiết kế (DRC) là nền tảng của xác minh vật lý. Phần mềm DRC quét mọi góc của bố cục chip để tìm các vi phạm, các đặc điểm có thể gây ra khuyết tật, giảm sản lượng hoặc đơn giản là làm cho thiết kế không thể sản xuất được. Nhưng các chip ngày nay không chỉ lớn hơn; chúng còn phức tạp hơn, được dệt từ nhiều lớp logic, bộ nhớ và các thành phần tương tự, đôi khi được xếp chồng lên nhau theo ba chiều. Các quy tắc cũng không đơn giản. Chúng có thể phụ thuộc vào hình học, ngữ cảnh, quy trình sản xuất và thậm chí là các tương tác giữa các đặc điểm bố cục xa nhau.

Truyền thống, DRC được thực hiện muộn trong quy trình, khi tất cả các thành phần được lắp ráp vào bố cục chip cuối cùng. Tại giai đoạn này, thường phát hiện hàng triệu vi phạm và việc sửa chữa những vấn đề muộn này đòi hỏi nỗ lực lớn, dẫn đến những trì hoãn tốn kém. Để giảm thiểu gánh nặng này, ngày càng có nhiều sự chú ý vào việc chuyển DRC sớm hơn trong quy trình, một chiến lược gọi là "shift-left." Thay vì chờ đợi cho đến khi toàn bộ thiết kế hoàn tất, các kỹ sư cố gắng xác định và giải quyết các lỗi DRC sớm hơn nhiều ở cấp độ khối và ô. Cách tiếp cận thiết kế và xác minh đồng thời này cho phép phần lớn các lỗi được phát hiện khi việc sửa chữa nhanh hơn và ít gây rối hơn.

Tuy nhiên, việc chạy DRC sớm hơn trong quy trình trên một chip đầy đủ khi các khối không sạch DRC tạo ra các tập dữ liệu kết quả có quy mô đáng kinh ngạc, thường là hàng chục triệu đến hàng tỷ "lỗi," cảnh báo hoặc cờ vì thiết kế chip chưa hoàn thiện là "bẩn" so với một chip đã trải qua quy trình thiết kế đầy đủ. Điều hướng những kết quả "bẩn" này là một thách thức riêng. Các nhà thiết kế phải ưu tiên các vấn đề nào cần giải quyết, xác định các mẫu chỉ ra các vấn đề hệ thống và quyết định điều gì thực sự quan trọng. Trong nhiều trường hợp, công việc này chậm và "thủ công," phụ thuộc vào khả năng của các kỹ sư để sắp xếp dữ liệu, lọc những gì quan trọng và chia sẻ phát hiện giữa các nhóm.

Để đối phó, các nhóm thiết kế đã tạo ra những cách để hạn chế dòng thông tin. Họ có thể giới hạn số lượng lỗi theo quy tắc, hoặc sử dụng các cách tắt không chính thức chuyển các cơ sở dữ liệu hoặc ảnh chụp màn hình qua email cho các thành viên trong nhóm, chia sẻ bộ lọc trong tin nhắn trò chuyện và dựa vào các chuyên gia để biết nơi cần tìm. Tuy nhiên, cách tiếp cận này không bền vững. Nó có nguy cơ bỏ lỡ các vấn đề lớn, toàn chip có thể lan tỏa qua sản phẩm cuối cùng. Nó làm chậm phản ứng và khiến việc hợp tác trở nên tốn công sức.

Với những thách thức về nguồn nhân lực đang diễn ra và sự phức tạp gia tăng của các chip hiện đại, nhu cầu về phân tích DRC thông minh hơn, tự động hóa hơn trở nên cấp bách. Vậy một giải pháp tốt hơn sẽ trông như thế nào và AI có thể giúp lấp đầy khoảng trống này như thế nào?

Những đột phá gần đây trong AI đã thay đổi cuộc chơi cho phân tích DRC theo những cách mà trước đây không thể tưởng tượng nổi. Thay vì quét từng dòng hoặc từng kiểm tra, các hệ thống được trang bị AI có thể xử lý hàng tỷ lỗi, nhóm chúng thành các nhóm có ý nghĩa và giúp các nhà thiết kế tìm ra nguyên nhân gốc rễ nhanh hơn nhiều. Những công cụ này sử dụng các kỹ thuật từ thị giác máy tính, học máy tiên tiến và phân tích dữ liệu lớn để biến những gì từng có vẻ như một đống thông tin không thể xử lý thành một lộ trình hành động.

Khả năng của AI trong việc tổ chức các tập dữ liệu hỗn loạn, tìm ra các vấn đề hệ thống ẩn giấu qua nhiều quy tắc hoặc khu vực giúp phát hiện các rủi ro mà việc lọc cơ bản có thể bỏ lỡ. Bằng cách nhóm các lỗi liên quan và làm nổi bật các điểm nóng, các nhà thiết kế có thể thấy bức tranh tổng thể và tập trung thời gian của họ vào những nơi quan trọng. Các thuật toán phân nhóm dựa trên AI chuyển đổi một cách đáng tin cậy hàng tuần điều tra thủ công thành vài phút phân tích có hướng dẫn.

Một lợi ích khác: sự hợp tác. Bằng cách coi kết quả là các tập dữ liệu sống chia sẻ thay vì các bảng tĩnh các công cụ hiện đại cho phép các nhóm chỉ định chủ sở hữu, chú thích phát hiện và chuyển giao các góc nhìn phân tích chính xác giữa các kỹ sư khối và phân vùng, thậm chí qua các ranh giới tổ chức. Các dấu trang động và trạng thái giao diện người dùng chia sẻ giảm thiểu sự nhầm lẫn và công việc làm lại. Thay vì "trở lại và đi tới," các nhóm tiến về phía trước cùng nhau.

Nhiều đổi mới này gợi ý về những gì có thể xảy ra khi AI được tích hợp vào trung tâm của quy trình xác minh. Không chỉ giúp các nhà thiết kế phân tích kết quả; chúng còn giúp mọi người lý luận về dữ liệu, tóm tắt phát hiện và đưa ra quyết định thiết kế tốt hơn cho đến khi hoàn tất.

Một trong những ví dụ nổi bật nhất về phân tích DRC được trang bị AI đến từ Siemens, nền tảng Calibre Vision AI của họ đang thiết lập các tiêu chuẩn mới cho cách xác minh chip toàn diện diễn ra. Dựa trên nhiều năm kinh nghiệm trong xác minh vật lý, Siemens nhận ra rằng việc phá vỡ các nút thắt không chỉ cần các thuật toán thông minh hơn mà còn cần suy nghĩ lại cách các nhóm làm việc cùng nhau và cách dữ liệu di chuyển qua quy trình.

Vision AI được thiết kế cho tốc độ và khả năng mở rộng. Nó sử dụng một cơ sở dữ liệu lỗi gọn nhẹ và một động cơ đa luồng để tải hàng triệu, hoặc thậm chí hàng tỷ, lỗi trong vài phút, trực quan hóa chúng để các kỹ sư thấy các cụm và điểm nóng trên toàn bộ die. Thay vì một bức tường mã lỗi hoặc các vi phạm quy tắc riêng lẻ, công cụ này trình bày một bản đồ nhiệt của bố cục, làm nổi bật các khu vực có nồng độ vấn đề cao nhất. Bằng cách bật hoặc tắt các lớp (bố cục, dấu hiệu, bản đồ nhiệt) và điều chỉnh độ mờ của lớp, người dùng có được cái nhìn rõ ràng, tùy chỉnh về những gì đang diễn ra và nơi cần tìm tiếp theo.

Nhưng điều kỳ diệu thực sự nằm ở việc phân nhóm được hướng dẫn bởi AI. Sử dụng các thuật toán học máy tiên tiến, Vision AI phân tích từng lỗi để tìm các nhóm có nguyên nhân thất bại chung. Điều này có nghĩa là các nhà thiết kế có thể tấn công nguyên nhân gốc rễ một lần, sửa chữa các vấn đề cho hàng trăm kiểm tra cùng một lúc thay vì phải giải quyết từng cái một một cách tỉ mỉ. Trong những trường hợp mà các công cụ kế thừa buộc các nhóm phải vật lộn với, ví dụ, 3.400 kiểm tra với 600 triệu lỗi, việc phân nhóm của Vision AI có thể giảm nỗ lực đó xuống chỉ còn 381 nhóm biến những ngọn núi thành những đống đất nhỏ và tăng tốc thời gian gỡ lỗi ít nhất gấp đôi.

Vision AI cũng rất hợp tác. Các dấu trang động ghi lại trạng thái chính xác của phân tích, từ bộ lọc lớp đến các khu vực bố cục đã phóng to, cùng với các chú thích và phân công chủ sở hữu. Chia sẻ một dấu trang gửi một phân tích sống động không chỉ là một bức ảnh tĩnh đến đồng nghiệp, vì vậy mọi người đều làm việc từ cùng một góc nhìn. Các nhóm có thể xuất cơ sở dữ liệu kết quả, phân phối các nhóm có thể hành động cho các chủ sở hữu khối, và nhập liền mạch các phát hiện vào các công cụ EDA khác của Siemens để gỡ lỗi thêm.

Một điểm đau thường gặp trong xác minh chip là nhu cầu về chuyên môn sâu biết lỗi nào quan trọng, mẫu nào có nghĩa là rắc rối và cách diễn giải các kết quả phức tạp. Calibre Vision AI giúp san bằng sân chơi. Các thuật toán dựa trên AI của nó nhất quán tạo ra cùng một cụm và lộ trình gỡ lỗi mà các chuyên gia cao cấp sẽ xác định, nhưng làm điều đó trong vài phút. Người dùng mới có thể nhanh chóng tìm ra các vấn đề hệ thống và hoạt động như những kỹ sư dày dạn kinh nghiệm, giúp các công ty chip giải quyết tình trạng thiếu hụt nguồn nhân lực và sự thay đổi nhân sự.

Ngoài các cụm và dấu trang, Vision AI cho phép các nhà thiết kế xây dựng các tín hiệu tùy chỉnh bằng cách tận dụng dữ liệu của riêng họ. Nền tảng này bảo vệ các mô hình và dữ liệu của khách hàng để sử dụng độc quyền, đảm bảo thông tin nhạy cảm vẫn nằm trong công ty. Và bằng cách tích hợp với hệ sinh thái AI EDA của Siemens, Calibre Vision AI hỗ trợ các chatbot AI sinh và trợ lý lý luận. Các nhà thiết kế có thể đặt câu hỏi trực tiếp về cú pháp, về một tín hiệu, về quy trình và nhận được câu trả lời chính xác kịp thời, giúp đơn giản hóa việc đào tạo và áp dụng.

Phản hồi từ khách hàng từ các công ty IC hàng đầu cho thấy giá trị thực tế của AI cho phân tích DRC và gỡ lỗi chip toàn diện. Một công ty báo cáo rằng Vision AI đã giảm nỗ lực gỡ lỗi của họ ít nhất một nửa một lợi ích tạo ra sự khác biệt giữa việc hoàn tất và trì hoãn. Một công ty khác lưu ý rằng thuật toán tín hiệu của nền tảng tự động tạo ra cùng một nhóm kiểm tra mà những người dùng có kinh nghiệm sẽ xác định thủ công, tiết kiệm không chỉ thời gian mà còn cả năng lượng.

Những lợi ích định lượng là rất ấn tượng. Ví dụ, Calibre Vision AI có thể tải và trực quan hóa các tệp lỗi nhanh hơn đáng kể so với các quy trình gỡ lỗi truyền thống. Một ví dụ cho thấy sự khác biệt trong bốn trường hợp thử nghiệm khác nhau: một tệp kết quả mất 350 phút với quy trình truyền thống, nhưng chỉ mất 31 phút với Calibre Vision AI. Trong một trường hợp thử nghiệm khác (không được hiển thị), chỉ mất năm phút để phân tích và phân nhóm 3,2 tỷ lỗi từ hơn 380 kiểm tra quy tắc thành 17 nhóm có ý nghĩa. Thay vì bị lạc trong hàng gigabyte dữ liệu lỗi, các nhà thiết kế giờ đây có thể dành thời gian giải quyết các vấn đề thực sự.

Ngày nay, các chip đòi hỏi nhiều hơn những cải tiến từng bước trong phần mềm EDA. Khi nhu cầu về tốc độ, chất lượng và sự hợp tác tiếp tục gia tăng, câu chuyện về xác minh vật lý sẽ được định hình bởi các công nghệ thông minh hơn, thích ứng hơn. Với phân tích DRC được trang bị AI, chúng ta thấy một con đường rõ ràng: một cách nhanh hơn và hiệu quả hơn để tìm ra các vấn đề hệ thống, gỡ lỗi thông minh, hợp tác mạnh mẽ hơn và cơ hội cho mọi nhà thiết kế tạo ra ảnh hưởng như một chuyên gia.

Bằng cách kết hợp sự sáng tạo của các kỹ sư với tốc độ và cái nhìn sâu sắc của AI, các nền tảng như Calibre Vision AI đang thúc đẩy một đường cong năng suất mới trong phân tích chip toàn diện. Với những công cụ này, các nhóm không chỉ theo kịp sự phức tạp, họ biến nó thành một lợi thế cạnh tranh.

Tại Siemens, tương lai của xác minh chip đã bắt đầu hình thành, nơi trí tuệ làm việc song song với trực giác, và những ý tưởng mới tìm đường đến silicon nhanh hơn bao giờ hết. Khi ngành công nghiệp tiếp tục đẩy mạnh các ranh giới và mở khóa thế hệ thiết bị tiếp theo, AI sẽ giúp thiết kế chip đạt đến những tầm cao mới.

Một làn sóng thay đổi lớn đang diễn ra trong toàn bộ lĩnh vực tự động hóa thiết kế điện tử (EDA), lĩnh vực phần mềm và công cụ chuyên biệt mà các nhà sản xuất chip sử dụng để thiết kế, phân tích và xác minh các mạch tích hợp phức tạp bên trong các chip hiện nay. Trí tuệ nhân tạo (AI) đã bắt đầu tác động đến nhiều phần của quy trình thiết kế chip—giúp việc bố trí và định tuyến, dự đoán kết quả sản xuất, điều chỉnh các mạch tương tự, tự động hóa mô phỏng và thậm chí hướng dẫn lập kế hoạch kiến trúc ban đầu. Thay vì chỉ đơn thuần tăng tốc các bước cũ, AI đang mở ra những cách suy nghĩ và làm việc mới.

Các mô hình học máy có thể giúp dự đoán các điểm nóng về khuyết tật hoặc ưu tiên các khu vực rủi ro từ rất sớm trước khi gửi chip đi sản xuất. Thay vì sử dụng tính toán brute-force hay hàng triệu dòng mã tùy chỉnh, AI sử dụng các thuật toán tiên tiến để phát hiện các mẫu, tổ chức các tập dữ liệu khổng lồ và làm nổi bật các vấn đề mà nếu không sẽ mất hàng tuần làm việc thủ công để phát hiện. Ví dụ, AI sinh (generative AI) có thể giúp các nhà thiết kế đặt câu hỏi và nhận câu trả lời bằng ngôn ngữ tự nhiên, giúp đơn giản hóa các nhiệm vụ thường nhật.

Sự hợp tác ngày càng tăng giữa chuyên môn con người và trí tuệ máy móc đang mở đường cho cái mà một số người gọi là cuộc cách mạng "shift left" hay xây dựng đồng thời tìm và sửa chữa các vấn đề sớm hơn trong quy trình thiết kế, trước khi chúng trở thành những trở ngại tốn kém. Đối với các nhà sản xuất chip, điều này có nghĩa là chất lượng cao hơn và thời gian ra thị trường nhanh hơn. Đối với các nhà thiết kế, điều này có nghĩa là có cơ hội tập trung vào đổi mới thay vì phải chạy theo các lỗi.

Khi các chip ngày càng phức tạp, phần thiết kế gọi là xác minh vật lý trở thành một nút thắt quan trọng. Xác minh vật lý kiểm tra xem bố cục chip có đáp ứng các quy tắc nghiêm ngặt của nhà sản xuất và trung thực khớp với sơ đồ chức năng ban đầu hay không. Mục tiêu chính của nó là đảm bảo rằng thiết kế có thể được sản xuất một cách đáng tin cậy thành một chip hoạt động, không có các khuyết tật vật lý có thể gây ra sự cố sau này.

Kiểm tra quy tắc thiết kế (DRC) là nền tảng của xác minh vật lý. Phần mềm DRC quét mọi góc của bố cục chip để tìm các vi phạm, các đặc điểm có thể gây ra khuyết tật, giảm sản lượng hoặc đơn giản là làm cho thiết kế không thể sản xuất được. Nhưng các chip ngày nay không chỉ lớn hơn; chúng còn phức tạp hơn, được dệt từ nhiều lớp logic, bộ nhớ và các thành phần tương tự, đôi khi được xếp chồng lên nhau theo ba chiều. Các quy tắc cũng không đơn giản. Chúng có thể phụ thuộc vào hình học, ngữ cảnh, quy trình sản xuất và thậm chí là các tương tác giữa các đặc điểm bố cục xa nhau.

Truyền thống, DRC được thực hiện muộn trong quy trình, khi tất cả các thành phần được lắp ráp vào bố cục chip cuối cùng. Tại giai đoạn này, thường phát hiện hàng triệu vi phạm và việc sửa chữa những vấn đề muộn này đòi hỏi nỗ lực lớn, dẫn đến những trì hoãn tốn kém. Để giảm thiểu gánh nặng này, ngày càng có nhiều sự chú ý vào việc chuyển DRC sớm hơn trong quy trình, một chiến lược gọi là "shift-left." Thay vì chờ đợi cho đến khi toàn bộ thiết kế hoàn tất, các kỹ sư cố gắng xác định và giải quyết các lỗi DRC sớm hơn nhiều ở cấp độ khối và ô. Cách tiếp cận thiết kế và xác minh đồng thời này cho phép phần lớn các lỗi được phát hiện khi việc sửa chữa nhanh hơn và ít gây rối hơn.

Tuy nhiên, việc chạy DRC sớm hơn trong quy trình trên một chip đầy đủ khi các khối không sạch DRC tạo ra các tập dữ liệu kết quả có quy mô đáng kinh ngạc, thường là hàng chục triệu đến hàng tỷ "lỗi," cảnh báo hoặc cờ vì thiết kế chip chưa hoàn thiện là "bẩn" so với một chip đã trải qua quy trình thiết kế đầy đủ. Điều hướng những kết quả "bẩn" này là một thách thức riêng. Các nhà thiết kế phải ưu tiên các vấn đề nào cần giải quyết, xác định các mẫu chỉ ra các vấn đề hệ thống và quyết định điều gì thực sự quan trọng. Trong nhiều trường hợp, công việc này chậm và "thủ công," phụ thuộc vào khả năng của các kỹ sư để sắp xếp dữ liệu, lọc những gì quan trọng và chia sẻ phát hiện giữa các nhóm.

Để đối phó, các nhóm thiết kế đã tạo ra những cách để hạn chế dòng thông tin. Họ có thể giới hạn số lượng lỗi theo quy tắc, hoặc sử dụng các cách tắt không chính thức chuyển các cơ sở dữ liệu hoặc ảnh chụp màn hình qua email cho các thành viên trong nhóm, chia sẻ bộ lọc trong tin nhắn trò chuyện và dựa vào các chuyên gia để biết nơi cần tìm. Tuy nhiên, cách tiếp cận này không bền vững. Nó có nguy cơ bỏ lỡ các vấn đề lớn, toàn chip có thể lan tỏa qua sản phẩm cuối cùng. Nó làm chậm phản ứng và khiến việc hợp tác trở nên tốn công sức.

Với những thách thức về nguồn nhân lực đang diễn ra và sự phức tạp gia tăng của các chip hiện đại, nhu cầu về phân tích DRC thông minh hơn, tự động hóa hơn trở nên cấp bách. Vậy một giải pháp tốt hơn sẽ trông như thế nào và AI có thể giúp lấp đầy khoảng trống này như thế nào?

Những đột phá gần đây trong AI đã thay đổi cuộc chơi cho phân tích DRC theo những cách mà trước đây không thể tưởng tượng nổi. Thay vì quét từng dòng hoặc từng kiểm tra, các hệ thống được trang bị AI có thể xử lý hàng tỷ lỗi, nhóm chúng thành các nhóm có ý nghĩa và giúp các nhà thiết kế tìm ra nguyên nhân gốc rễ nhanh hơn nhiều. Những công cụ này sử dụng các kỹ thuật từ thị giác máy tính, học máy tiên tiến và phân tích dữ liệu lớn để biến những gì từng có vẻ như một đống thông tin không thể xử lý thành một lộ trình hành động.

Khả năng của AI trong việc tổ chức các tập dữ liệu hỗn loạn, tìm ra các vấn đề hệ thống ẩn giấu qua nhiều quy tắc hoặc khu vực giúp phát hiện các rủi ro mà việc lọc cơ bản có thể bỏ lỡ. Bằng cách nhóm các lỗi liên quan và làm nổi bật các điểm nóng, các nhà thiết kế có thể thấy bức tranh tổng thể và tập trung thời gian của họ vào những nơi quan trọng. Các thuật toán phân nhóm dựa trên AI chuyển đổi một cách đáng tin cậy hàng tuần điều tra thủ công thành vài phút phân tích có hướng dẫn.

Một lợi ích khác: sự hợp tác. Bằng cách coi kết quả là các tập dữ liệu sống chia sẻ thay vì các bảng tĩnh các công cụ hiện đại cho phép các nhóm chỉ định chủ sở hữu, chú thích phát hiện và chuyển giao các góc nhìn phân tích chính xác giữa các kỹ sư khối và phân vùng, thậm chí qua các ranh giới tổ chức. Các dấu trang động và trạng thái giao diện người dùng chia sẻ giảm thiểu sự nhầm lẫn và công việc làm lại. Thay vì "trở lại và đi tới," các nhóm tiến về phía trước cùng nhau.

Nhiều đổi mới này gợi ý về những gì có thể xảy ra khi AI được tích hợp vào trung tâm của quy trình xác minh. Không chỉ giúp các nhà thiết kế phân tích kết quả; chúng còn giúp mọi người lý luận về dữ liệu, tóm tắt phát hiện và đưa ra quyết định thiết kế tốt hơn cho đến khi hoàn tất.

Một trong những ví dụ nổi bật nhất về phân tích DRC được trang bị AI đến từ Siemens, nền tảng Calibre Vision AI của họ đang thiết lập các tiêu chuẩn mới cho cách xác minh chip toàn diện diễn ra. Dựa trên nhiều năm kinh nghiệm trong xác minh vật lý, Siemens nhận ra rằng việc phá vỡ các nút thắt không chỉ cần các thuật toán thông minh hơn mà còn cần suy nghĩ lại cách các nhóm làm việc cùng nhau và cách dữ liệu di chuyển qua quy trình.

Vision AI được thiết kế cho tốc độ và khả năng mở rộng. Nó sử dụng một cơ sở dữ liệu lỗi gọn nhẹ và một động cơ đa luồng để tải hàng triệu, hoặc thậm chí hàng tỷ, lỗi trong vài phút, trực quan hóa chúng để các kỹ sư thấy các cụm và điểm nóng trên toàn bộ die. Thay vì một bức tường mã lỗi hoặc các vi phạm quy tắc riêng lẻ, công cụ này trình bày một bản đồ nhiệt của bố cục, làm nổi bật các khu vực có nồng độ vấn đề cao nhất. Bằng cách bật hoặc tắt các lớp (bố cục, dấu hiệu, bản đồ nhiệt) và điều chỉnh độ mờ của lớp, người dùng có được cái nhìn rõ ràng, tùy chỉnh về những gì đang diễn ra và nơi cần tìm tiếp theo.

Nhưng điều kỳ diệu thực sự nằm ở việc phân nhóm được hướng dẫn bởi AI. Sử dụng các thuật toán học máy tiên tiến, Vision AI phân tích từng lỗi để tìm các nhóm có nguyên nhân thất bại chung. Điều này có nghĩa là các nhà thiết kế có thể tấn công nguyên nhân gốc rễ một lần, sửa chữa các vấn đề cho hàng trăm kiểm tra cùng một lúc thay vì phải giải quyết từng cái một một cách tỉ mỉ. Trong những trường hợp mà các công cụ kế thừa buộc các nhóm phải vật lộn với, ví dụ, 3.400 kiểm tra với 600 triệu lỗi, việc phân nhóm của Vision AI có thể giảm nỗ lực đó xuống chỉ còn 381 nhóm biến những ngọn núi thành những đống đất nhỏ và tăng tốc thời gian gỡ lỗi ít nhất gấp đôi.

Vision AI cũng rất hợp tác. Các dấu trang động ghi lại trạng thái chính xác của phân tích, từ bộ lọc lớp đến các khu vực bố cục đã phóng to, cùng với các chú thích và phân công chủ sở hữu. Chia sẻ một dấu trang gửi một phân tích sống động không chỉ là một bức ảnh tĩnh đến đồng nghiệp, vì vậy mọi người đều làm việc từ cùng một góc nhìn. Các nhóm có thể xuất cơ sở dữ liệu kết quả, phân phối các nhóm có thể hành động cho các chủ sở hữu khối, và nhập liền mạch các phát hiện vào các công cụ EDA khác của Siemens để gỡ lỗi thêm.

Một điểm đau thường gặp trong xác minh chip là nhu cầu về chuyên môn sâu biết lỗi nào quan trọng, mẫu nào có nghĩa là rắc rối và cách diễn giải các kết quả phức tạp. Calibre Vision AI giúp san bằng sân chơi. Các thuật toán dựa trên AI của nó nhất quán tạo ra cùng một cụm và lộ trình gỡ lỗi mà các chuyên gia cao cấp sẽ xác định, nhưng làm điều đó trong vài phút. Người dùng mới có thể nhanh chóng tìm ra các vấn đề hệ thống và hoạt động như những kỹ sư dày dạn kinh nghiệm, giúp các công ty chip giải quyết tình trạng thiếu hụt nguồn nhân lực và sự thay đổi nhân sự.

Ngoài các cụm và dấu trang, Vision AI cho phép các nhà thiết kế xây dựng các tín hiệu tùy chỉnh bằng cách tận dụng dữ liệu của riêng họ. Nền tảng này bảo vệ các mô hình và dữ liệu của khách hàng để sử dụng độc quyền, đảm bảo thông tin nhạy cảm vẫn nằm trong công ty. Và bằng cách tích hợp với hệ sinh thái AI EDA của Siemens, Calibre Vision AI hỗ trợ các chatbot AI sinh và trợ lý lý luận. Các nhà thiết kế có thể đặt câu hỏi trực tiếp về cú pháp, về một tín hiệu, về quy trình và nhận được câu trả lời chính xác kịp thời, giúp đơn giản hóa việc đào tạo và áp dụng.

Phản hồi từ khách hàng từ các công ty IC hàng đầu cho thấy giá trị thực tế của AI cho phân tích DRC và gỡ lỗi chip toàn diện. Một công ty báo cáo rằng Vision AI đã giảm nỗ lực gỡ lỗi của họ ít nhất một nửa một lợi ích tạo ra sự khác biệt giữa việc hoàn tất và trì hoãn. Một công ty khác lưu ý rằng thuật toán tín hiệu của nền tảng tự động tạo ra cùng một nhóm kiểm tra mà những người dùng có kinh nghiệm sẽ xác định thủ công, tiết kiệm không chỉ thời gian mà còn cả năng lượng.

Những lợi ích định lượng là rất ấn tượng. Ví dụ, Calibre Vision AI có thể tải và trực quan hóa các tệp lỗi nhanh hơn đáng kể so với các quy trình gỡ lỗi truyền thống. Một ví dụ cho thấy sự khác biệt trong bốn trường hợp thử nghiệm khác nhau: một tệp kết quả mất 350 phút với quy trình truyền thống, nhưng chỉ mất 31 phút với Calibre Vision AI. Trong một trường hợp thử nghiệm khác (không được hiển thị), chỉ mất năm phút để phân tích và phân nhóm 3,2 tỷ lỗi từ hơn 380 kiểm tra quy tắc thành 17 nhóm có ý nghĩa. Thay vì bị lạc trong hàng gigabyte dữ liệu lỗi, các nhà thiết kế giờ đây có thể dành thời gian giải quyết các vấn đề thực sự.

Ngày nay, các chip đòi hỏi nhiều hơn những cải tiến từng bước trong phần mềm EDA. Khi nhu cầu về tốc độ, chất lượng và sự hợp tác tiếp tục gia tăng, câu chuyện về xác minh vật lý sẽ được định hình bởi các công nghệ thông minh hơn, thích ứng hơn. Với phân tích DRC được trang bị AI, chúng ta thấy một con đường rõ ràng: một cách nhanh hơn và hiệu quả hơn để tìm ra các vấn đề hệ thống, gỡ lỗi thông minh, hợp tác mạnh mẽ hơn và cơ hội cho mọi nhà thiết kế tạo ra ảnh hưởng như một chuyên gia.

Bằng cách kết hợp sự sáng tạo của các kỹ sư với tốc độ và cái nhìn sâu sắc của AI, các nền tảng như Calibre Vision AI đang thúc đẩy một đường cong năng suất mới trong phân tích chip toàn diện. Với những công cụ này, các nhóm không chỉ theo kịp sự phức tạp, họ biến nó thành một lợi thế cạnh tranh.

Tại Siemens, tương lai của xác minh chip đã bắt đầu hình thành, nơi trí tuệ làm việc song song với trực giác, và những ý tưởng mới tìm đường đến silicon nhanh hơn bao giờ hết. Khi ngành công nghiệp tiếp tục đẩy mạnh các ranh giới và mở khóa thế hệ thiết bị tiếp theo, AI sẽ giúp thiết kế chip đạt đến những tầm cao mới.