From Beijing with Love

Cháu đã lớn thế này rồi à. Lại đây chú ôm cái coi.

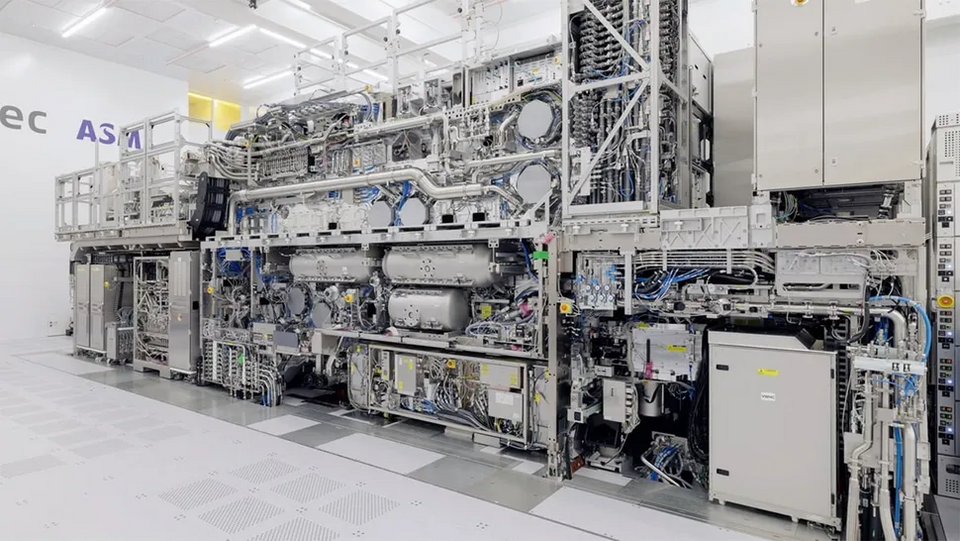

TSMC đã tái khẳng định chiến lược không sử dụng công cụ quang khắc High-NA EUV cho các công nghệ tiên tiến sắp tới gồm A16 (1.6nm) và A14 (1.4nm). Thay vào đó, TSMC sẽ tiếp tục tối ưu hóa các công cụ Low-NA EUV hiện tại để đạt hiệu quả mong muốn về hiệu suất, công suất và mật độ transistor. Phát biểu của Phó Chủ tịch Điều hành và Phó Tổng Giám đốc Phát triển Kinh doanhKevin Zhang đã làm sáng tỏ cách tiếp cận này, nhấn mạnh sự đổi mới của đội ngũ kỹ thuật TSMC trong việc kéo dài tuổi thọ của công nghệ hiện có.

TSMC tuyên bố các công nghệ A16 (ra mắt 2027) và A14 (sản xuất đại trà 2028) không yêu cầu High-NA EUV, hệ thống quang khắc tiên tiến với độ phân giải 8nm, mà vẫn đảm bảo cải tiến vượt bậc. Kevin Zhang cho biết: “Khi High-NA mang lại lợi ích đáng kể, chúng tôi sẽ áp dụng. Với A14, đội ngũ đã đạt được những cải tiến bộ lớn mà không cần High-NA.” A16 thực chất là phiên bản cải tiến của N2P, tích hợp Super Power Rail (SPR) để tăng hiệu suất. Vì N2 và N2P chỉ cần Low-NA EUV (độ phân giải 13.5nm), A16 cũng không cần nâng cấp công cụ.

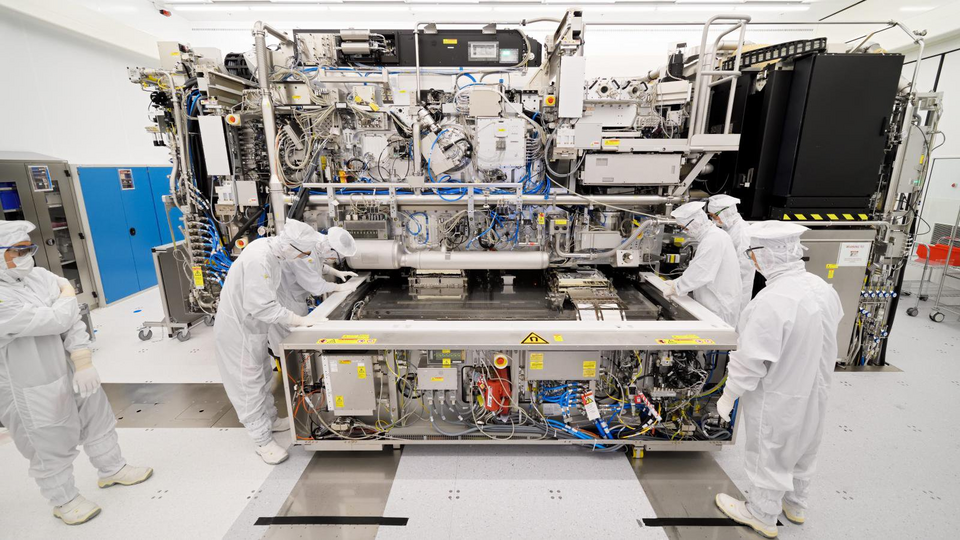

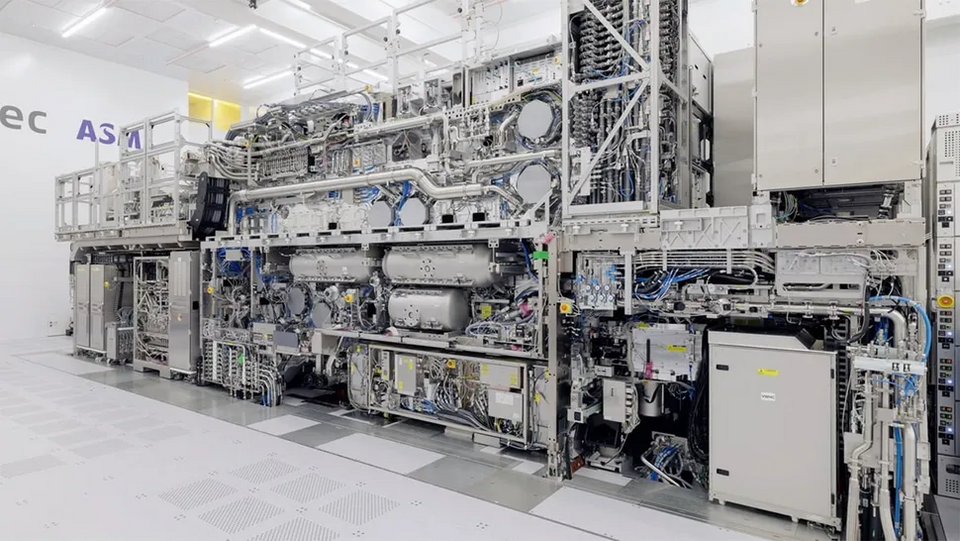

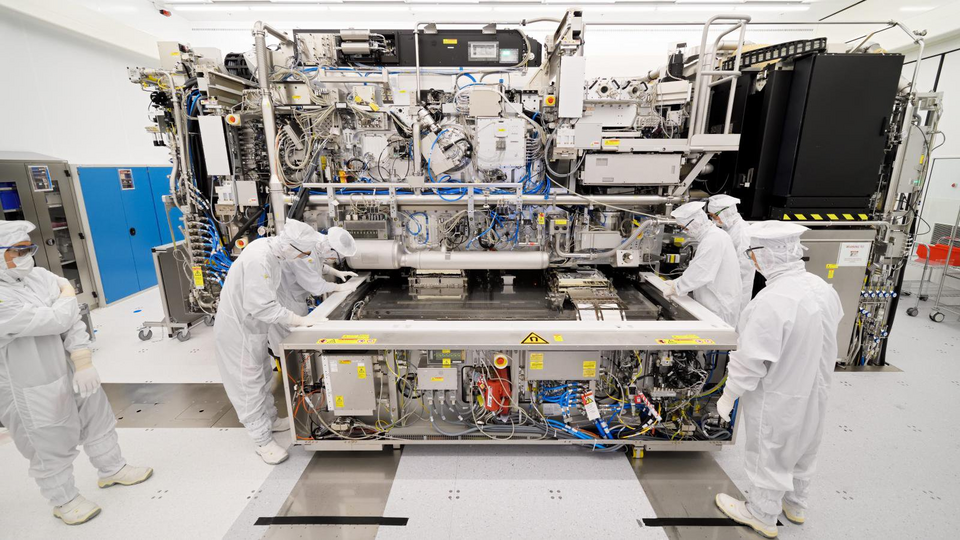

Đội ngũ kỹ thuật của TSMC đã phát triển các giải pháp sáng tạo để đạt mật độ và hiệu suất cao mà không phụ thuộc vào High-NA. Zhang từ chối tiết lộ chi tiết về việc sử dụng multi-patterning (đa lớp mẫu) cho A14, nhưng nhấn mạnh rằng công ty đã tìm ra cách sản xuất chip 1.4nm với Low-NA EUV. Điều này giúp giảm chi phí đầu tư vào công cụ High-NA, vốn đắt đỏ (khoảng 400 triệu USD/máy so với 150 triệu USD cho Low-NA).

A14 sử dụng transistor nanosheet gate-all-around (GAA) thế hệ hai và kiến trúc ô tiêu chuẩn mới, mang lại cải tiến đáng kể. So với N2, A14 tăng 15% hiệu suất ở cùng mức công suất, hoặc giảm 25-30% công suất ở cùng tần số. Về mật độ transistor, A14 đạt tăng 20% cho cấu hình hỗn hợp (logic/SRAM/analog) và 23% cho logic thuần. Đây là lợi thế của một nút công nghệ hoàn chỉnh, ngang với bước nhảy từ 3nm sang 2nm.

A14 là một nút công nghệ hoàn toàn mới, dự kiến sản xuất đại trà vào 2028, phục vụ các chip AI, điện thoại, và máy chủ. Việc không cần High-NA cho A14 là minh chứng cho khả năng đổi mới của TSMC, khi các đối thủ như Intel phải dựa vào High-NA để giảm bước quy trình cho 14A (2027-2028). TSMC còn lên kế hoạch ra mắt A14 với SPR vào 2029, tích hợp mạng cấp nguồn mặt sau, và có vẻ cũng không cần High-NA.

Không giống TSMC, Intel dự kiến áp dụng High-NA EUV cho công nghệ 14A vào 2027-2028, nhằm giảm số lần phơi sáng EUV (multi-patterning) và đơn giản hóa quy trình. High-NA cho phép Intel đạt độ phân giải cao hơn, phù hợp với chiến lược “lấy lại vị thế” trước TSMC và Samsung. Tuy nhiên, chi phí đầu tư lớn và rủi ro kỹ thuật (High-NA là công nghệ mới) có thể làm Intel gặp khó nếu triển khai không suôn sẻ.

Bằng cách kéo dài tuổi thọ của Low-NA EUV, TSMC tiết kiệm chi phí đầu tư cơ sở hạ tầng, đồng thời duy trì lợi thế cạnh tranh về giá. Zhang nhấn mạnh: “Chúng tôi sẽ dùng High-NA khi tìm được điểm giao thoa tối ưu, mang lại lợi ích và ROI cao nhất.” Chiến lược này phù hợp với mô hình foundry của TSMC, phục vụ nhiều khách hàng lớn như Apple, Nvidia, AMD, với yêu cầu chi phí thấp và năng suất cao.

Việc tiếp tục sử dụng Low-NA EUV cho A14 có thể làm tăng độ phức tạp của multi-patterning, dẫn đến thời gian sản xuất lâu hơn và rủi ro lỗi cao hơn. TSMC cần đảm bảo năng suất (yield) ổn định để đáp ứng đơn hàng từ các “ông lớn” như Qualcomm hay MediaTek. Ngoài ra, nếu đối thủ như Samsung áp dụng High-NA sớm hơn, TSMC có thể bị áp lực cạnh tranh về độ phân giải và hiệu suất chip.

Zhang thừa nhận TSMC sẽ sử dụng High-NA EUV vào một thời điểm nào đó, có thể sau 2030, khi công nghệ này ổn định và chi phí hợp lý hơn. Với kế hoạch mở rộng nhà máy tại Đức, Nhật Bản, và Arizona, TSMC đang chuẩn bị hạ tầng để tích hợp High-NA khi cần. Chiến lược “chờ thời điểm tối ưu” giúp TSMC tránh rủi ro công nghệ mới, đồng thời tận dụng tối đa Low-NA EUV.

Chiến lược của TSMC với A16 và A14 cho thấy sự tự tin vào khả năng đổi mới kỹ thuật, không phụ thuộc vào công cụ đắt đỏ như High-NA EUV. Bằng cách tối ưu Low-NA EUV và phát triển transistor nanosheet, TSMC duy trì vị thế dẫn đầu trong ngành bán dẫn, phục vụ nhu cầu AI, 5G, và điện toán đám mây. So với Intel, TSMC chọn con đường tiết kiệm chi phí và ổn định năng suất, phù hợp với vai trò foundry toàn cầu. Với A14 SPR vào 2029, TSMC tiếp tục định hình tương lai chip, có thể trì hoãn High-NA đến A12 hoặc xa hơn.

TSMC tuyên bố các công nghệ A16 (ra mắt 2027) và A14 (sản xuất đại trà 2028) không yêu cầu High-NA EUV, hệ thống quang khắc tiên tiến với độ phân giải 8nm, mà vẫn đảm bảo cải tiến vượt bậc. Kevin Zhang cho biết: “Khi High-NA mang lại lợi ích đáng kể, chúng tôi sẽ áp dụng. Với A14, đội ngũ đã đạt được những cải tiến bộ lớn mà không cần High-NA.” A16 thực chất là phiên bản cải tiến của N2P, tích hợp Super Power Rail (SPR) để tăng hiệu suất. Vì N2 và N2P chỉ cần Low-NA EUV (độ phân giải 13.5nm), A16 cũng không cần nâng cấp công cụ.

Đội ngũ kỹ thuật của TSMC đã phát triển các giải pháp sáng tạo để đạt mật độ và hiệu suất cao mà không phụ thuộc vào High-NA. Zhang từ chối tiết lộ chi tiết về việc sử dụng multi-patterning (đa lớp mẫu) cho A14, nhưng nhấn mạnh rằng công ty đã tìm ra cách sản xuất chip 1.4nm với Low-NA EUV. Điều này giúp giảm chi phí đầu tư vào công cụ High-NA, vốn đắt đỏ (khoảng 400 triệu USD/máy so với 150 triệu USD cho Low-NA).

A14 sử dụng transistor nanosheet gate-all-around (GAA) thế hệ hai và kiến trúc ô tiêu chuẩn mới, mang lại cải tiến đáng kể. So với N2, A14 tăng 15% hiệu suất ở cùng mức công suất, hoặc giảm 25-30% công suất ở cùng tần số. Về mật độ transistor, A14 đạt tăng 20% cho cấu hình hỗn hợp (logic/SRAM/analog) và 23% cho logic thuần. Đây là lợi thế của một nút công nghệ hoàn chỉnh, ngang với bước nhảy từ 3nm sang 2nm.

A14 là một nút công nghệ hoàn toàn mới, dự kiến sản xuất đại trà vào 2028, phục vụ các chip AI, điện thoại, và máy chủ. Việc không cần High-NA cho A14 là minh chứng cho khả năng đổi mới của TSMC, khi các đối thủ như Intel phải dựa vào High-NA để giảm bước quy trình cho 14A (2027-2028). TSMC còn lên kế hoạch ra mắt A14 với SPR vào 2029, tích hợp mạng cấp nguồn mặt sau, và có vẻ cũng không cần High-NA.

Không giống TSMC, Intel dự kiến áp dụng High-NA EUV cho công nghệ 14A vào 2027-2028, nhằm giảm số lần phơi sáng EUV (multi-patterning) và đơn giản hóa quy trình. High-NA cho phép Intel đạt độ phân giải cao hơn, phù hợp với chiến lược “lấy lại vị thế” trước TSMC và Samsung. Tuy nhiên, chi phí đầu tư lớn và rủi ro kỹ thuật (High-NA là công nghệ mới) có thể làm Intel gặp khó nếu triển khai không suôn sẻ.

Bằng cách kéo dài tuổi thọ của Low-NA EUV, TSMC tiết kiệm chi phí đầu tư cơ sở hạ tầng, đồng thời duy trì lợi thế cạnh tranh về giá. Zhang nhấn mạnh: “Chúng tôi sẽ dùng High-NA khi tìm được điểm giao thoa tối ưu, mang lại lợi ích và ROI cao nhất.” Chiến lược này phù hợp với mô hình foundry của TSMC, phục vụ nhiều khách hàng lớn như Apple, Nvidia, AMD, với yêu cầu chi phí thấp và năng suất cao.

Việc tiếp tục sử dụng Low-NA EUV cho A14 có thể làm tăng độ phức tạp của multi-patterning, dẫn đến thời gian sản xuất lâu hơn và rủi ro lỗi cao hơn. TSMC cần đảm bảo năng suất (yield) ổn định để đáp ứng đơn hàng từ các “ông lớn” như Qualcomm hay MediaTek. Ngoài ra, nếu đối thủ như Samsung áp dụng High-NA sớm hơn, TSMC có thể bị áp lực cạnh tranh về độ phân giải và hiệu suất chip.

Zhang thừa nhận TSMC sẽ sử dụng High-NA EUV vào một thời điểm nào đó, có thể sau 2030, khi công nghệ này ổn định và chi phí hợp lý hơn. Với kế hoạch mở rộng nhà máy tại Đức, Nhật Bản, và Arizona, TSMC đang chuẩn bị hạ tầng để tích hợp High-NA khi cần. Chiến lược “chờ thời điểm tối ưu” giúp TSMC tránh rủi ro công nghệ mới, đồng thời tận dụng tối đa Low-NA EUV.

Chiến lược của TSMC với A16 và A14 cho thấy sự tự tin vào khả năng đổi mới kỹ thuật, không phụ thuộc vào công cụ đắt đỏ như High-NA EUV. Bằng cách tối ưu Low-NA EUV và phát triển transistor nanosheet, TSMC duy trì vị thế dẫn đầu trong ngành bán dẫn, phục vụ nhu cầu AI, 5G, và điện toán đám mây. So với Intel, TSMC chọn con đường tiết kiệm chi phí và ổn định năng suất, phù hợp với vai trò foundry toàn cầu. Với A14 SPR vào 2029, TSMC tiếp tục định hình tương lai chip, có thể trì hoãn High-NA đến A12 hoặc xa hơn.